# 복소결합부하를 이용한 3.5 GHz 대역의 고효율 비대칭 도허티 전력증폭기 설계

# 3.5 GHz High-Efficiency Asymmetric Doherty Power Amplifier Design Using a Complex Combining Load

김주성\*·최우진·최영찬·오한식·양영구

Joosung Kim\* · Woojin Choi · Youngchan Choi · Hansik Oh · Youngoo Yang

요 약

본 논문에서는 복소결합부하(complex combining load)를 이용한 3.5 GHz 대역의 비대칭 도허티 전력증폭기를 설계하였다. 복소결합부하를 이용하면 일반 DPA 구조 대비, 더 높은 OBO(output back-off)를 가질 수 있고, 적절한 리액턴스 값선정에 따라 부하 변조 구간에서 효율 개선도 가능하다. 또한 비대칭 구조를 같이 적용하여 최대 출력지점에서 carrier와 peaking amplifier가 같은 전류를 가지므로 매칭 회로 설계가 용이하도록 구현하였다. 기존 복소결합부하 논문에서는 출력 매칭 회로가 성능에 매우 중요한 영향을 주지만 ABCD parameter로만 제시되어 실제 구현이 어려운 점이 있어 본 논문에서는 Smith chart를 이용한 매칭을 통해 직관적인 방법을 제시하였고, 회로 소형화를 위해 매칭 구조를 개선하였다. 제작된 비대칭 CCL DPA는 CW 기준, 3.5~3.6 GHz 대역에서 42.0~43.0 dBm 최대 출력전력, 60~64.7 % DE 그리고 54.8~59.9 % PAE를 보여준다. 7~8 dB back-off 지점인 35.0 dBm에서 51.3~51.6 % DE 그리고 46.7~47.6 % PAE를 가진다. LTE 20 MHz 변조신호 인가 시, 평균 출력전력 35.0 dBm에서 10.7~11.5 dB 전력이득, 48.1~48.5 % DE, 44.0~45.1 % PAE 그리고 31.1 dBc의 ACLR을 얻었고 추가적으로 DPD를 적용하여 49.3~50.4 dBc로 개선하였다.

#### **Abstract**

In this study, a high-efficiency asymmetric Doherty power amplifier (DPA) based on a complex combining load (CCL) is presented. The CCL method extends the range of output back-off (OBO). This article provides a graphical design method using the Smith chart for the CCL-DPA load network. The proposed asymmetric DPA is designed using 6 and 10 W GaN-HEMTs for carrier and peaking amplifiers, respectively. With 3.5 ~ 3.6 GHz continuous-wave signal excitations, the implemented asymmetric CCL DPA exhibits a DE of 60.0 ~ 64.7 % and a PAE of 54.8 ~ 59.9 % at a maximum output power of 42.0 ~ 43.0 dBm. In addition, it has a DE of 51.3 ~ 51.6 %, and a PAE of 46.7 ~ 47.6 % at an output power of 35.0 dBm. Using an LTE signal with a PAPR of 7.5 dB and a signal bandwidth of 20 MHz, a power gain of 10.7 ~ 11.5 dB, a PAE of 44.0 ~ 45.1 %, a DE of 48.1 ~ 48.5 %, and an ACLR of -31.1 dBc are achieved. Using DPD linearization, ACLR is improved to -49.3/-50.4 dBc at an average power of 35.0 dBm.

Key words: Complex Combining Load (CCL), Doherty Power Amplifiers (DPAs), Asymmetric DPA, 3.5 GHz, Smith Chart.

<sup>「</sup>이 성과는 2019년도 정부(과학기술정보통신부)의 재원으로 한국연구재단의 지원을 받아 수행된 연구임(2018R1A2B3005479).」

성균관대학교 전자전기컴퓨터공학과(Department of Electrical and Computer Engineering, Sungkyunkwan University)

<sup>\*</sup>성균관대학교 DMC공학과(Department of Digital Media Communication Engineering, Sungkyunkwan University)

<sup>·</sup> Manuscript received May 28, 2021; Revised July 4, 2021; Accepted July 27, 2021. (ID No. 20210528-056)

<sup>·</sup> Corresponding Author: Youngoo Yang (e-mail: yang09@skku.edu)

# Ⅰ. 서 론

최근 5G 통신기술이 상용화되면서 AR/VR 및 홀로그램 등 대용량의 서비스를 제공하기 위해 OFDM 기반에서 256-QAM과 같은 매우 높은 modulation order가 요구되고 있다. 다만 OFDM waveform의 단점으로는 PAPR(peak-to-average power ratio)이 높아 이로 인해 송신기는 최대전력이 아닌 OBO(output back-off)에서 동작해야만 하고, 따라서 평균전력에서의 효율이 급감하는 문제가 있다. 또한 RF power amplifier의 경우 일반적으로 단말기 내의 부품중 가장 큰 전력을 사용함으로 발열 및 소모전류 측면에서 높은 효율을 필수적으로 만족해야 한다[1],[2].

고효율의 RF PA 설계를 위해 DPA(Doherty power amplifier), ET(envelope tracking) 등 다양한 방법이 연구되어 왔다. 먼저 DPA의 경우, 1936년 W.H Doherty에 의해 개 발된 구조로 현재 대부분의 기지국 PA에서 적용하고 있 는 구조이다<sup>[3]</sup>. Carrier amplifier와 peaking amplifier를 병렬 로 연결한 단순한 구조지만 결합점에서의 부하 변조(load modulation)를 통한 OBO의 확장이 가능하여 이를 통해 우리가 원하는 평균전력에서의 효율 저하를 개선할 수 있다. 다만 기본적인 DPA 구조에서는 이론적으로 6 dB의 OBO를 넘을 수 없다. 따라서 OBO의 증가를 위해 다양한 연구가 진행되어왔고 Multi-way DPA, Asymmetric DPA, 복소결합부하(CCL) 등이 있다<sup>[4]~[9]</sup>. 특히 CCL 구조의 경 우, 결합점에 일반적인 저항성 부하가 아닌 복소부하를 사용하여, OBO를 늘리는 새로운 방법을 제시하였다. 복 소부하를 사용하면 리액턴스 성분의 존재로 인해 부하변 조 시, 일반적인 DPA 대비, 더 높은 OBO를 가질 수 있고, DPA의 문제 중 하나인 부하 변조 구간에서 효율이 저하 되는 부분에 대해 개선도 가능하다[7],[8]. 다만 일반적인 Class AB-C bais 구조에서 peaking amplifier의 출력전류가 부족한 부분이 있어 본 논문에서는 비대칭 구조를 적용 한 CCL DPA 설계를 통해 3.5 GHz 대역에서 9 dB OBO를 목표로 하는 고효율 전력증폭기를 설계를 진행하였다.

#### Ⅱ. 회로 설계 및 시뮬레이션

#### 2-1 회로 설계

본 논문에서 목표로 하는 9 dB의 OBO를 만족하기 위

한 결합점의 복소부하( $Z_L$ )는 참고문헌 [7]의 수식을 이용하여 구할 수 있다. 이를 위해 먼저 CCL DPA의 변조비 ( $\beta$ )는 식 (1)을 통해 구할 수 있다.

$$OBO = 10\log(2\beta). \tag{1}$$

계산한 변조비를 식 (2)에 적용하여 복소부하의 저항 성분 $(R_L)$ 과 리액턴스 성분 $(X_L)$ 의 비 $(x_n)$ 를 구할 수 있다.

$$x_n = \sqrt{\frac{(2\beta - 1)(\beta - 2)}{\beta}} \ . \tag{2}$$

여기서  $R_L$ 의 경우, carrier와 peaking amplifier의 최대 출력지점에서의 부하 임피던스 $(R_{opt})$ 에 맞춰 설계자유도가 있는 값이다. 추후 매칭 및 실제 구현이 쉬운 값으로 선택할 수 있다. 본 논문에서는 ADS simulation의 load pull을 통해 구한 carrier amplifier(CGH4006P)와 peaking amplifier (CGH40010F)의 최적 임피던스는 다음과 같다.  $(R_{opt,c}=35\ \Omega,\ R_{opt,p}=30\ \Omega)$  그리고 매칭 과정에서 복소결합부하의 저항 성분인  $R_L$ 은 15  $\Omega$ 으로 선정하였다.

#### 2-2 CCL 출력 매칭회로 구현

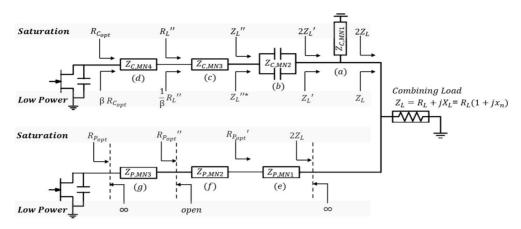

먼저 carrier amplifier는 low power와 saturation 영역 모 두에서 우리가 원하는 임피던스로 매칭이 되어야 함으로 출력 매칭 회로(OMN)가 매우 중요하다. 기존의 CCL DPA의 연구<sup>[7]</sup>에서는 출력 매칭 회로에 대해서는 ideal case에 대해 ABCD parameter로만 제시되어 있어 이를 토 대로 실제 microstrip 및 lumped element를 이용하여 OMN 를 구현할 경우, 어떠한 방법으로 매칭을 해야 하는지에 대한 구체적인 설명이 부족하다. 이를 보완하여 최근의 연구<sup>[10]</sup>에서는 CCL DPA의 OMN에 대해 smith chart를 이 용한 graphical method를 제시하였다. 다만 해당 논문의 OMN의 경우, series TL 3개를 이용하여 매칭함으로 필연 적으로 대역폭이 좁은 한계를 가지고 있다. 본 연구에서 는 이를 개선한 매칭 회로를 제시한다. CCL DPA의 출력 매칭 회로의 전체적인 구성은 그림 1과 같다. 참고문헌 [10]과 달리 본 논문에서는 (a), (b) 단계에서 series TL이 아닌 shunt L + series C 구조를 이용하여 기존 대비 회로 를 소형화하여 구현하였다. 각 매칭 단계는 다음과 수식 을 이용하여 순차적으로 구할 수 있다.

그림 1. CCL DPA 출력 매칭 회로

Fig. 1. Load network of the CCL DPA.

$$Z_{C,MN1} = \sqrt{2} |Z_L|. (3)$$

$$Z_{C,MN2} = -j \left( \frac{1}{wC_{MN2}} \right). \tag{4}$$

$$Z_{C,MN3} = |Z_L''|. (5)$$

$$Z_{C,MN4} = \sqrt{R_L'' R_{opt,c}}.$$

(6)

$$Z_{P,MN} = |2Z_L|. (7)$$

$$Z_{P,MN2} = R_P. (8)$$

$$Z_{P,MN3} = \sqrt{R_P R_{P_{obt}}}.$$

(9)

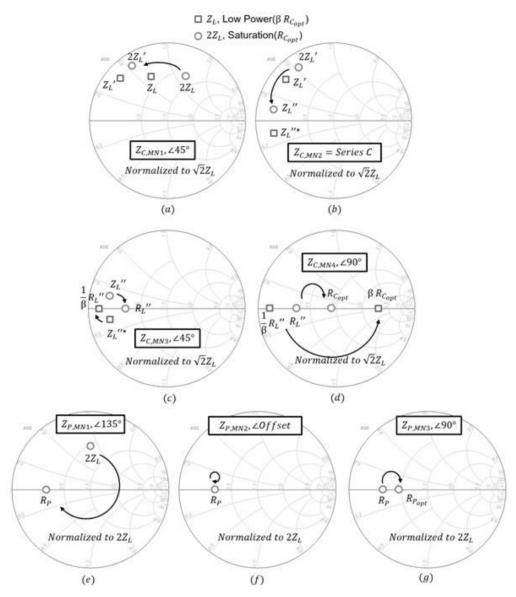

그림 2에서는 그림 1에서의 (a)~(f), 각 매칭 단계를 smith chart를 활용하여 직관적으로 표현하였다.

먼저 carrier amplifier의 출력 임피던스 매칭 회로에 대해 알아보면 다음과 같다.

- (a) Shunt L 라인( $Z_{C,MM} \angle 45^\circ$ )을 이용하여 low power 영역에서의  $Z_L$  및 saturation의  $2Z_L$ 을 같은 저항값( $R_L'$ )을 가지는 지점  $Z_L'$ 과  $2Z_L'$ 으로 이동한다.

- (b) Series  $C(C_{MN2})$ 를 이용하여  $Z_L'$ 과  $2Z_L'$ 의 리액턴스 값 변경을 통해 complex conjugate인  $Z_L''*$ 과  $Z_L''$ 으로 변환한다. 이때의  $C_{MN2}$ 은 앞에서 구한  $Z_L'$ ,  $2Z_L'$ 의 리액턴스 값인  $X_{Z_L}$ ,  $X_{2Z_L}$  및 식 (10)을 이용하여  $C_{MN2}$ 을 구할 수 있다. 다만 실제 구현 시에는 상용 소자의 S-parameter를 이

용하여 설계하였고 수식으로 계산된 값과 시뮬레이션 상의 차이가 발생함으로 병렬 cap 구조를 이용하여 오차를 최소로 설계하였다.

$$C_{MN2} = \frac{2}{w(X_{Z_L} + X_{2Z_L})} \tag{10}$$

- (c) Series  $\mathrm{TL}(Z_{C,MN3}\angle$  45 °)을 통해  $Z_L^{\prime\prime}*$ 과  $Z_L^{\prime\prime}$ 을 순수한 저항값을 가지는  $\frac{1}{\beta}R_L^{\prime\prime},~R_L^{\prime\prime}$ 로 변경한다.

- (d) Series  $\mathrm{TL}(Z_{C,MN4}\angle 90\,^\circ)$ 을 통해  $\frac{1}{\beta}R_L'',R_L''$ 을 최종 목표인  $\beta R_{C_{o,\mu}},\ R_{C_{o,\mu}}$ 로 변환한다. Peaking amplifer의 출력 임피던스 매칭도 동일하게 그림 2를 참고하여 series TL 3개를 이용하여 설계하면 다음과 같다.

- (e) Series  $TL(Z_{P,MM} \angle 135^{\circ})$ 을 통해 saturation에서의  $2Z_I$ 을 순수한 저항값을 가지는 지점인  $R_P$ 로 이동한다.

- (f) Offset  $line(Z_{P,MN2} \angle offset)$ 을 통해 peaking amplifier는 low power에서 결합점에서 바라본 임피던스가 open  $(\infty)$ 이 되어야 함으로 이를 맞춰준다. 이때 임피던스인  $R_P$ 의 변화는 없다.

- (g) Series  $\mathrm{TL}(Z_{P,MN3}\angle 90^\circ)$ 을 이용하여  $R_P$ 를 우리가 원하는 peaking amplifer의 최적 임피던스 지점인  $R_{P_{opt}}$ 로 변화한다.

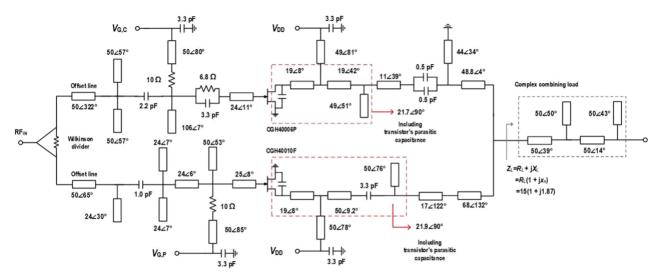

그림 3은 본 논문에서 설계한 비대칭 CCL DPA의 전체 회로도를 보여준다. 입력신호는 Wilkinson divider를 통해

그림 2. CCL DPA의 Carrier 및 Peaking의 출력 임피던스 매칭 과정: (a) Carrier 매칭1, (b) Carrier 매칭2, (c) Carrier 매칭3, (d) Carrier 매칭4, (e) Peaking 매칭1, (f) Peaking 매칭2, (g) Peaking 매칭3

Fig. 2. Design procedure of the load network of the CCL DPA: (a) Carrier MN1, (b) Carrier MN2, (c) Carrier MN3, (d) Carrier MN4, (e) Peaking MN1, (f) Peaking MN2, (g) Peaking MN3.

동일하게 입력되며(1:1) 별도의 offset 라인을 이용하여 carrier와 peaking의 출력 전류의 위상을 맞춰준다. 그 후 입력 매칭 회로를 통해 각 트랜지스터의 최적 입력 임피던스로 변환된다. 안정성 확보를 위해 gate bias 회로에는 직렬로 10 Ω을 추가하였고 carrier amplifier의 입력에는

6.8  $\Omega$ 과 3.3 pF 병렬회로를 삽입하였다. 또한 입력과 출력 임피던스의 경우, 효율 개선을 위해 설계 주파수인 3.5 GHz에서  $2^{nd}$  고조파 임피던스를 단락하기 위해  $\lambda/4$ 라인을 이용한 bias 회로로 구성하였다. 마지막으로 결합점에서 50  $\Omega$ 까지의 CCL 부분의 매칭 회로는 넓은 대역폭을

그림 3. 설계한 비대칭 CCL DPA 전체 회로도

Fig. 3. Schematic of the overall asymmetric CCL DPA.

위해 single section이 아닌 2-section으로 구현하였다.

# Ⅲ. 제작 및 측정 결과

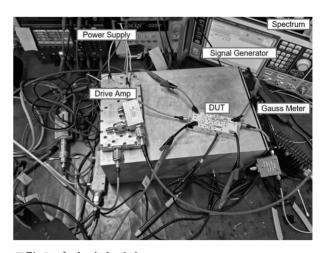

그림 4는 본 논문에서 실제로 제작하고 측정한 비대칭 CCL DPA를 보여준다. PCB는 Rogers Ro4350B이고 기판의 유전율을 3.78 그리고 동박 두께는 20 mils이다. 전체 PCB size는  $112 \times 55 \text{ mm}^2$ 로 설계되었다. ADS 2019를 통해설계한 입력과 출력 매칭 회로는  $3.5 \sim 3.6 \text{ GHz}$ 까지 넓은 대역폭 확보를 위해 HFSS 시뮬레이션을 통해 추가적인 최적화를 진행하였다. gate bias의 경우, carrier는 -2.8 V,

그림 4. 제작된 비대칭 CCL DPA

Fig. 4. Photograph of the implemented asymmetric CCL DPA.

peaking의 경우 -6.3 V이고, drain voltage는 모두 28 V로 설정하였다. 이때의 carrier amplifier의 quiescent current  $(I_Q)$ 는 41 mA이다. 측정 장비 셋업은 그림 5와 같이 signal generator에서 발생한 신호를 별도의 drive amplifier를 이용하여 증폭하여 입력신호로 사용하였다. 측정은 signal generator의 입력전력을 조절하면서 측정하고자 하는 DUT를 통과한 신호 spectrum analyzer를 이용하여 출력전력을 측정하였고, gauss meter 및 power supply를 통해 drain current를 측정하였다. 이를 통해 원하는 대역의

그림 5. 측정 장비 셋업

Fig. 5. Photograph of the measurement setup.

power gain, DE 및 PAE를 계산하였다.

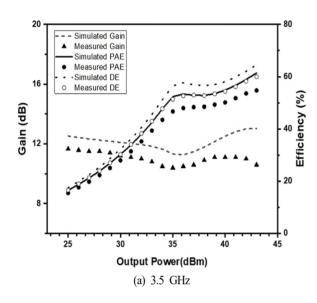

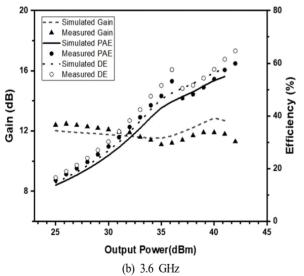

그림 6은 continuous-wave(CW) 신호를 이용하여 측정된 power gain, DE 그리고 PAE를 보여준다. 3.5 GHz 대역에서는 최대 출력지점인 43.0 dBm에서 10.6 dB의 power gain, 60 %의 DE 그리고 54.8 %의 PAE를 보여준다. 또한 8 dB backoff 된 지점인 출력전력 35.0 dBm에서는 10.4

그림 6. 시뮬레이션과 CW 신호를 이용하여 측정한 Gain, PAE 그리고 DE

Fig. 6. Simulated and measured gain, PAE and DE using the CW signal.

dB의 power gain과 51.3%의 DE 그리고 46.7 %의 PAE를 가진다. 또한 3.6 GHz 대역에서는 최대 출력지점인 42.0 dBm에서 11.3 dB의 power gain, 64.7 %의 DE 그리고 59.9 %의 PAE를 보여준다. 또한 7 dB backoff 한 출력전력 35.0 dBm에서는 11.1 dB의 power gain과 51.6 %의 DE 그리고 47.6 %의 PAE를 가진다.

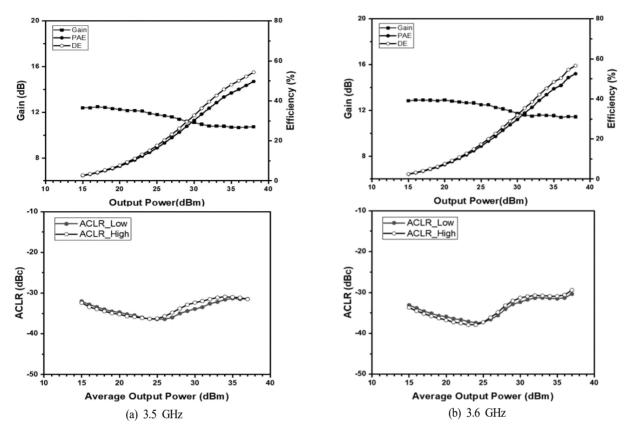

그림 7은 LTE 20 MHz 변조신호를 이용하여 측정된 power gain, DE, PAE 그리고 ACLR을 보여준다. 3.5 GHz 대역에서는 평균 출력전력 35.0 dBm에서 10.7 dB의 power gain, 48.1 %의 DE, 44.0 %의 PAE 그리고 ACLR -31.1 dBc를 보여준다. 3.6 GHz 대역에서는 평균출력전력 35.0 dBm(OBO 7 dB)에서 11.5 dB의 power gain, 48.5 %의 DE, 45.1 %의 PAE 그리고 ACLR -31.1 dBc를 가진다.

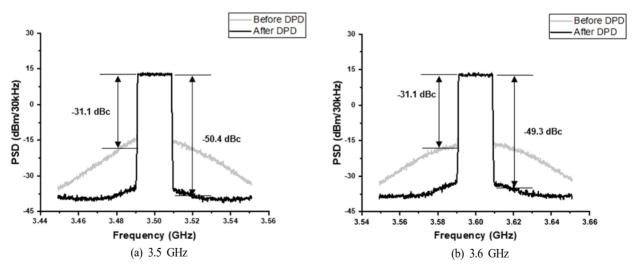

그림 8에서는 DPD 적용 전/후 측정결과를 보여준다. 3.5 GHz 대역에서는 평균 출력전력 35.0 dBm 기준, ACLR 이 -50.4 dBc로 19.3 dB 개선된다. 3.6 GHz 대역에서는 ACLR이 18.2 dB 개선되어 -49.3 dBc로 측정되었다.

### Ⅳ. 결 론

본 논문에서는 3.5~3.6 GHz에서 동작하는 비대칭 복 소부하결합 도허티 전력증폭기를 설계하였다. 복소결합 부하를 이용하면 기존의 DPA 대비 더 넓은 OBO와 부하 변조 구간에서 효율 개선이 가능하다. 기존의 CCL DPA 논문의 경우, 성능에 가장 중요한 영향을 주는 매칭 회로 에 대한 설명이 ABCD parameter로 제시되어 실제 구현이 난해한 점이 있었다. 본 논문에서는 RF 공학자에게 친숙 한 Smith chart를 이용하여 직관적으로 설계할 수 있고, 기존의 논문 대비 회로를 소형화한 매칭 회로를 개선하 였다. 표 1에서 정리한 것과 같이 설계된 비대칭 CCL DPA는 CW 기준, 3.5~3.6 GHz 대역에서 42.0~43.0 dBm 최대 출력전력, 60~64.7 % DE 그리고 54.8~59.9 % PAE 를 보여준다. 7~8 dB back-off 지점인 35.0 dBm에서 51. 3~51.6 % DE 그리고 46.7~47.6 % PAE를 보여준다. LTE 20 MHz 변조신호의 경우, 평균 출력전력 35.0 dBm 에서 10.7~11.5 dB 전력이득, 48.1~48.5 % DE, 44.0~ 45.1 % PAE 그리고 -31.1 dBc의 ACLR을 가진다. DPD 를 적용 시, -49.3~50.4 dBc로 개선됨을 확인하였다.

그림 7. 20 MHz LTE 신호를 이용한 측정한 gain, PAE, DE 그리고 ACLR

Fig. 7. Measured performances of gain, PAE, DE, and ACLR using 20 MHz LTE signal.

그림 8. LTE 20 MHz 변조신호를 이용한 DPD 전/후 측정

Fig. 8. Measured power spectral density using 20 MHz LTE modulation signal before and after DPD.

| Ħ | 1 | 이정 | 여구 | 결과들과의 | 비교 |

|---|---|----|----|-------|----|

|   |   |    |    |       |    |

Table 1. Performance comparison to the previous works

| Ref.         | Freq<br>(GHz) | Topology       | VDD<br>(V) | Gain<br>(dB) | P <sub>sat</sub> (dBm) | P <sub>age</sub> (dBm) | OBO<br>(dB) | PAE<br>(%) | DE<br>(%) | ACLR<br>(dBC) | PAPR (dB) | Signal<br>BW<br>(MHz) | Signal<br>type |

|--------------|---------------|----------------|------------|--------------|------------------------|------------------------|-------------|------------|-----------|---------------|-----------|-----------------------|----------------|

| [7]          | 2.0           | Symmetric CCL  | 28         | 12.2         | 42.3                   | 33.2                   | 9.1         | N/A        | 57        | -23           | 9.6       | 5                     | WCDMA          |

| [8]          | 1.35~1.7      | Symmetric CCL  | 28/32      | 14~16        | <42                    | <33                    | 9           | N/A        | 50~56     | -34/-54       | 8.6       | 20                    | LTE            |

| [10]         | 1.68          | Asymmetric CCL | 28         | 13.5         | 43.5                   | 34                     | 9.5         | 53.6       | 56.4      | -27/-48       | 9.6       | 10                    | LTE            |

| [11]         | 3.3~3.6       | Asymmetric     | 28         | 11~13        | 41~42                  | 34                     | 7~8         | 36~45      | N/A       | -25.6         | -         | 10                    | LTE            |

| This<br>work | 3.5~3.6       | Asymmetric CCL | 28         | 10.7~11.5    | 42~43                  | 35                     | 7~8         | 44~45      | 48~48.5   | -31/-50.4     | 7.5       | 20                    | LTE            |

#### References

- [1] S. C. Cripps, RF Power Amplifiers for Wireless Communications, Norwood, MA, Artech House, 1999.

- [2] B. Kim, Doherty Power Amplifiers: From Fundamentals to Advanced Design Methods, San Diego, CA, Academic Press, Mar. 2018.

- [3] W. H. Doherty, "A new high efficiency power amplifier for modulated waves," *Proceedings of the IEEE*, vol. 24, pp. 1163-1182, Sep. 1936.

- [4] Y. Yang, J. Cha, B. Shin, and B. Kim, "A fully matched N-way Doherty amplifier with optimized linearity," *IEEE Transactions on Microwave Theory and Techniques*, vol. 51, no. 3, pp. 986-993, Mar. 2003.

- [5] H. Oh, H. Kang, H. Lee, H. Koo, M. Kim, and W. Lee, et al., "Doherty power amplifier based on the fundamental current ratio for asymmetric cells," *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 11, pp. 4190-4197, Nov. 2017.

- [6] B. Kim, J. Kim, I. Kim, and J. Cha, "The Doherty power amplifier," *IEEE Micro Magazine*, vol. 7, no. 5, pp. 42-50, Oct. 2006.

- [7] X. H. Fang, K. K. M. Cheng, "Extension of high-

- efficiency range of Doherty amplifier by using complex combining load," *IEEE Transactions on Microwave Theory and Techniques*, vol. 62, no. 9, pp. 2038-2047, Sep. 2014.

- [8] X. H. Fang, H. Y. Liu, K. K. M. Cheng, and S. Boumaiza, "Two-way Doherty power amplifier efficiency enhancement by incorporating transistor' nonlinear phase distortion," *IEEE Microwave and Wireless Components Letters*, vol. 28, no. 2, pp. 168-170, Feb. 2018.

- [9] R. Darraji, F. M. Ghannouchi, and O. Hammi, "A dual-input digitally driven Doherty amplifier architecture for performance enhancement of Doherty transmitters," *IEEE Transactions on Microwave Theory and Tech*niques, vol. 59, no. 5, pp. 1284-1293, May. 2011.

- [10] W. Choi, H. Kang, H. Oh, K. C. Hwang, K. Y. Lee, and Y. Yang, "Doherty power amplifier based on asymmetric cells with complex combining load," *IEEE Tran*sactions on Microwave Theory and Techniques, vol. 69, no. 4, pp. 2336-2344, Apr. 2021.

- [11] B. Wang, J. Teng, D. Zhang, and D. Su, "Design of a high-efficiency broadband asymmetric Doherty power amplifier," *Progress in Electromagnetics Research*, vol. 92, pp. 227-238, May. 2019.

#### 김 주 성 [성균관대학교/석사과정]

http://orcid.org/0000-0001-7651-1964

2013년 2월: 중앙대학교 전자전기공학부 (공학사)

2013년 1월~현재: 삼성전자

2020년 3월~현재: 성균관대학교 DMC공 학과 석사과정

[주 관심분야] RF/mm-Wave Power Amplifier, mmWave Antenna Technique

#### 오 한 식 [성균관대학교/박사과정]

http://orcid.org/0000-0002-1815-6666

2016년 2월: 성균관대학교 전자전기공학 과 (공학사)

2016년 3월~현재: 성균관대학교 전자전 기컴퓨터공학과 박사과정

[주 관심분야] RF/mm-Wave Power Amplifier, Linearization and Efficiency Enhancement Techniques, Analog/Mixed- Signal IC

#### 최 우 진 [성균관대학교/박사과정]

http://orcid.org/0000-0003-4365-1519

2018년 2월: 성균관대학교 전자전기컴퓨 터공학부 (공학사)

2018년 3월~현재: 성균관대학교 전자전 기컴퓨터공학과 박사과정

[주 관심분야] RF Power Amplifiers for Basestations, Broadband and Techniques, and MMICs.

## 양 영 구 [성균관대학교/교수]

http://orcid.org/0000-0003-3463-0687

1997년 2월: 한양대학교 전자공학과 (공학 사)

2002년 2월: 포항공과대학교 전자전기공 학과 (공학박사)

2002년 3월~2002년 7월: 포항공과대학교 전자전기공학과 박사후 연구원

2002년 8월~2005년 2월: Skyworks Solu-

tions Inc., Senior Electronic Engineer

2005년 3월~현재: 성균관대학교 전자전기컴퓨터공학과 교수 [주 관심분야] 초고주파 회로 설계, 무선통신 송/수신기 시스템 설계, 비선형 회로 분석 및 시뮬레이션 기법 연구

# 최 영 찬 [성균관대학교/석사과정]

https://orcid.org/0000-0002-4510-4685

2020년 2월: 성균관대학교 전자전기공학 부 (공학사)

2020년 3월~현재: 성균관대학교 전자전 기컴퓨터공학과 석사과정

[주 관심분야] Design of RF Power Amplifier for Basestations, Broadband Techniques, and MMICs