# 병렬 분할된 CMOS 점증 단권변압기와 모델링

# Parallel-Segmented CMOS Step-Up Autotransformer and Modeling

아현진 · 소병차 · 류현식\* · 이옥구

Hyunjin Ahn · Byung Chan Son · Hyunsik Ryu\* · Ockgoo Lee

#### 유 약

본 논문에서는 임피던스 변환율을 개선하기 위한 병렬 분할된 CMOS 점증 단권변압기를 제안한다. 또한, 이에 상응하는 확장성이 있는 CMOS 공정을 사용한 병렬 분할 기법을 사용한 모델링이 개발되었다. 제안된 병렬 분할 기법의 모델링을 사용하여 병렬 분할된 단권변압기의 정확한 성능 예측이 가능하다. 병렬 분할된 점증 단권변압기는 표준 CMOS 65 nm 공정을 사용하여 제작되었다. 모델링된 결과는 측정된 결과와 우수한 일치를 보여준다. 제작된 1개/2개 병렬 분할된 CMOS 점증 단권변압기는 3 GHz 주파수에서 -1.21 dB/-1.54 dB의 최소삽입손실의 특성을 보이며, 50 Ω 임피던스가 9.5 Ω/6.1 Ω의 임피던스로 변환되어 보인다.

#### **Abstract**

In this study, a parallel-segmented complementary metal-oxide – semiconductor (CMOS) step-up autotransformer was developed to improve the impedance transformation ratio. In addition, a corresponding scalable segmentation-based model was developed on a CMOS case. The proposed segmentation-based model was used to predict the accurate performance of a parallel-segmented autotransformer. The parallel-segmented step-up autotransformer was fabricated through a standard 65 nm CMOS process. The modeled results showed good agreement with the measured results. The implemented one/two parallel-segmented CMOS step-up autotransformer changed the impedance from 50  $\Omega$  to 9.5  $\Omega$ /6.1  $\Omega$  with -1.21 dB/-1.54 dB minimum insertion loss at 3 GHz.

Key words: Autotransformer, CMOS, Power Amplifier, Impedance Transformation, Insertion Loss

## T 서 론

최근 고품질의 서비스를 제공하는 5G 이동통신에 대한 요구가 꾸준히 증가하고 있다. 이에 따라 가격을 줄일수 있는 CMOS 기술을 이용한 완전 집적화된 통신용 회로에 대한 필요성이 요구되고 있다. CMOS 공정을 이용한 완전 집적화된 통신용 회로의 구현에 있어서 가장 어

려운 부분 중 하나가 CMOS 공정을 이용한 전력증폭기의 설계이다. 특히 CMOS 공정을 이용한 전력증폭기의 성능에 가장 크게 영향을 주는 부분은 전력증폭기의 출력 정합 네트워크이다. 전력증폭기의 출력 정합 네트워크의 역할은 50 ♀ 출력 부하의 높은 값에서 임피던스 변환 역할을 통해 CMOS 소자 쪽으로 작은 임피던스 값을 제공해야 한다. 작은 임피던스 값으로 소자 쪽에 제공되어야 소

<sup>「</sup>이 과제는 부산대학교 기본연구지원사업(2년)에 의하여 연구되었음.」

부산대학교 전기공학과(Department of Electrical Engineering, Pusan National University)

<sup>\*</sup>알에프에이치아이씨(RFHIC)

<sup>·</sup> Manuscript received June 30, 2020; Revised August 24, 2020; Accepted September 8, 2020. (ID No. 20200630-054)

<sup>·</sup> Corresponding Author: Ockgoo Lee (e-mail: olee@pusan.ac.kr)

자 쪽에서 큰 전류의 공급이 가능해져 큰 전력의 생성이 가능하게 된다<sup>11</sup>. 또한 삽입손실(insertion loss)이 적어야 전력의 손실을 최소화하여 큰 출력을 출력 부하에 전달이 가능하다. 완전 집적화된 전력증폭기 구조를 위해 가장 많이 사용되는 구조는 변압기 기반 구조이다. 출력 정합 네트워크에 사용되는 변압기의 경우, 일반적인 이권선형태의 변압기가 가장 많이 사용되고 있다<sup>[2]~[8]</sup>. 이권선변압기 구조에서 임피던스 변환과 삽입손실의 최적화를위해 일차측이 병렬로 분할된 구조가 기존의 연구에서 제안되었다<sup>[9]</sup>.

상대적으로 작은 크기로 삽입손실이 작은 단권변압기기반 출력 정합 네트워크에 대한 구조도 최근 제안되었다 다 100~[12]. 또한, 일차측이 병렬로 분할된 InGaP/GaAs 공정을 활용한 단권변압기 구조가 제안되었다 13]. 하지만, 이 경우 InGaP/GaAs 공정을 사용하였으며, 간단한 형태의 등가회로로 분석이 되었다. CMOS 공정의 경우, InGaP/GaAs 공정과 비교해서 상대적으로 얇은 두께의 metal을 사용한다. InGaP/GaAs 공정 substrate의 경우, 어느 정도 유전체에 가까워 substrate에 의한 간섭효과 및 손실이 작다. 반면에 CMOS 공정의 경우, lossy한 substrate를 사용하므로 변압기 구조로 사용되는 metal과 substrate 사이의 간섭효과 및 손실이 상대적으로 크며, 이를 잘 반영하기 위한 모델링이 필요하다.

본 논문에서는 일차측이 1개 그리고 2개로 병렬된 분할된 단권변압기를 CMOS 65 nm 공정을 통해서 제작하였다. 병렬 분할 기법을 적용한 완전한 CMOS 공정 기반모델링 구조를 제안한다. 기가헤르츠 대역에서의 표피효과(skin effect)와 근접효과(proximity effect)에 대한 변압기특성을 반영하기 위한 블록이 모델링에 포함되었다. 또한, 높은 주파수에서의 CMOS substrate의 영향을 반영하기 위한 블록이 모델링에 포함되었다. 또한, 양호도(quality factor, Q)에 따른 임피던스 변환 특성을 분석하였다.

## Ⅱ. 병렬 분할된 CMOS 단권변압기와 모델링

2-1 기존의 병할 분할된 단권변압기의 등가회로도 = 활용한  $R_{IN}$

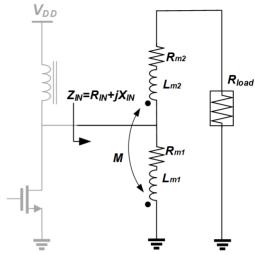

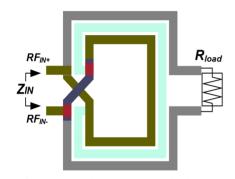

그림 1은 전력증폭기 출력 정합 네트워크의 적용을 바

- (a) 1개로 병렬 분할된 단권변압기의 등가회로도

- (a) Equivalent circuit of one parallel-segmented autotransformer

- (b) 2개로 병렬 분할된 단권변압기의 등가회로도

- (b) Equivalent circuit of two parallel-segmented autotransformer

- 그림 1. 병렬 분할된 단권변압기 등가회로도

Fig. 1. Equivalent circuits of parallel-segmented autotransformers.

탕으로 하는 병렬 분할된 점증 단권변압기의 등가회로도를 보여준다. 1차 측의 권선의 segment가 그림 1(a)의 경우, 1개이나, 그림 1(b)의 경우, 1차 측의 권선이 병렬로 분할되어 2개의 segment를 가지는 점증 단권변압기의 등 가회로도를 보여준다. 단권변압기의 경우, 1차 측 권선이 2차 측 권선의 한 부분으로 보여 일반적으로 사용되는 이

권선 변압기에 비해 턴 수가 작아 크기가 작아지며, 등가 회로의 직렬저항을 줄일 수 있어 손실이 상대적으로 작다 $^{[10]}$ . 그림 1에서  $Z_{IN}$ 은  $50 \Omega$  부하에서 변압기를 통해 변환된 변압기 입력 쪽으로 들여다본 임피던스이다. 그림 1에서  $L_{mI}$ 과  $R_{mI}$ 은 1차 측 segment의 등가 인덕턴스와 등가 저항을 나타내며,  $L_{m2}$ 와  $R_{m2}$ 는 2차 측 권선의 등가 인덕턴스와 등가 전화을 나타내며, M은 1차 측 segment와 2차 측권선 간의 상호 인덕턴스를 나타낸다. 1차 측 segment와 2차 측권선 간의 자기적인 결합으로 유기된 전압 관계를통해 단권변압기의  $Z_{IN}$ 은 각각의 파라미터의 관계식으로나타낼 수 있다.  $L_{mI} = L_{m2} = L_{m}$ 이고,  $R_{mI} = R_{m2} = R_{m}$ 인 경우, 1개의 segment로 병렬 분할된 점증 단권변압기  $Z_{IN}$ 의 실수부  $R_{IN}$ 은 식 (1)과 같이 표현된다 $^{[13]}$ .

$$\begin{split} R_{\in} &= R_m + [R_m (5\omega^2 L_m^2 + 9\omega^2 L_m M + 5\omega^2 M^2) \\ &+ (R_m + R_{load}) (\omega^2 L_m^2 + \omega^2 M^2 + \omega^2 M L_m) \\ &- R_{load} R_m^2 - 2R_m^3] / [(2R_m + R_{load})^2 + 4(\omega L_m + \omega M)^2] \end{split}$$

또한, 동일한 조건에서 2개 segment로 병렬 분할된 점 증 단권변압기의 경우 식 (2)와 같이 표현된다<sup>[13]</sup>.

$$\begin{split} R_{\in} &= (1/2)\,R_m + [R_m((7/8)\omega^2L_m^2 + 3\omega^2L_mM + (5/2)\omega^2M^2) \\ &+ (R_m + R_{load})((1/4)\omega^2L_m^2 + \omega^2M^2 + \omega^2ML_m) \\ &- (1/4)R_{load}R_m^2 - (3/8)R_m^3]/ \\ &[(3/2)R_m + R_{load})^2 + ((3/2)\omega L_m + 2\omega M)^2] \end{split} \tag{2}$$

## 2-2 병렬 분할 및 Q의 변화에 따른 병렬 분할된 단 권변압기의 RIN 분석

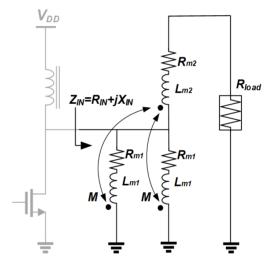

그림 2는  $50\ \Omega$  부하에  $L_m=0.8\ \mathrm{nH},\ R_m=\omega L_m/Q,\ 그리고$   $M=k(L_m\cdot L_m)^{1/2}(k=0.7)$ 의 일반적인 기가헤르츠(GHz) 대역의 단권변압기 레이아웃을 가정했을 때의 각각의 파라미터들을 바탕으로 위의 수식을 사용하여 얻은  $R_{IN}$ 의 그림이다. 1차 측이 2개로 병렬 분할된 2개의 segment로 구성된 점증 단권변압기는 1차 측이 1개로 병렬 분할된 1개의 segment로 구성된 점증변압기에 비해 더 낮은  $R_{IN}$ 으로 보이도록 구현될 수 있음을 확인할 수 있다. 이는 병렬 분할된 1 에 권선 점증 변압기와 동일하게 1차 측이 병렬로 분할되어 제공되는  $R_{IN}$ 이 작아지는 효과를 보이게 된다. 소자

그림 2. 병렬 분할 및 Q의 변화에 따른  $R_{IN}$ 에 대한 결과 Fig. 2. Results of  $R_{IN}$  according to variations of Q and number of segments.

에서 생성되는 전력  $P_{IN}$ 은  $R_{IN}$ 에 반비례한 관계를 보이며  $(P_{IN} \propto V_{DD}^2/R_{IN})^{[1]}$ , 따라서  $R_{IN}$ 이 작을수록 소자에서 더 큰 전류가 생성되어 더 큰 전력이 생성이 가능하게 된다. 양호도 Q는 metal 폭, 길이, 턴 수에 따라 가변적이며, 일반적인 CMOS 공정을 사용하는 경우, 대략 10 정도를 가정할 수 있다. 그림 2는 Q가 5, 10, 20인 경우의 변화에 따라  $R_{IN}$ 의 변화를 보여준다. Q가 낮을수록 상대적으로 동일한  $L_m$ 에 대해  $R_m$ 이 커지게 된다. 식 (1)과 식 (2)를 통해 첫번째 항이 1차 측  $R_m$ 에 대한 영향을 보여준다는 것을 확인할 수 있으며, 2개로 병렬 분할된 경우가 첫 번째 항이 반으로 줄게 됨을 확인할 수 있다. 또한, 그림 2에서 보이듯이 Q가 낮을수록  $R_m$ 이 커져  $R_{IN}$ 이 커져 보이게 된다.

#### 2-3 병렬 분할된 CMOS 단권변압기와 모델링

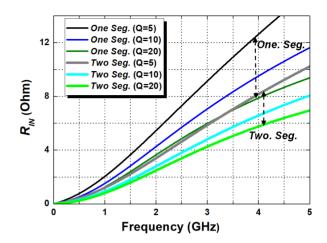

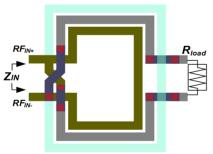

그림 3은 CMOS 표준 공정을 통해 제안된 병렬 분할된 차동 구조의 단권변압기의 레이아웃의 예를 보여준다. 그림 3에서 1차 측과 2차 측에서 각각 한 포트가 접지가 되면 그림 1과 같은 single-ended 구조가 된다. 병렬 분할된 단권변압기의 레이아웃은 3 GHz 전력증폭기의 출력 정합 네트워크용으로 설계되었다. 전력증폭기 구성 시 CMOS 소자가 1차 측에 연결되게 된다. 표준 CMOS 65 nm 공정에 제공되는 3.4  $\mu$ m 두께의 Cu top metal을 사용하여 lateral 형태의 단권변압기가 구성되었다. 그림 3(a)

- (a) 1개로 병렬 분할된 단권변압기의 레이아웃

- (a) Layout of one parallel-segmented autotransformer

- (b) 2개로 병렬 분할된 단권변압기의 레이아웃1

- (b) Layout1 of two parallel-segmented autotransformer

- (c) 2개로 병렬 분할된 단권변압기의 레이아웃2

- (c) Layout2 of two parallel-segmented autotransformer

- 그림 3. 병렬 분할된 단권변압기 레이아웃

Fig. 3. Layouts of parallel-segmented autotransformers.

는 1개의 segment로 병렬 분할된 단권변압기의 레이아웃을 보여준다. 2개의 병렬 분할을 위해 여러 위치에 추가적으로 1차 측 병렬 분할이 가능하다. 그림 3(b)는 1개의 segment로 병렬 분할된 단권변압기 구조에서 추가로 1차측과 2차 측 사이에 1차 측 병렬 분할이 추가되어 2개의 segment로 병렬 분할된 단권변압기의 레이아웃을 보여준

다. 그림 3(c)는 1개의 segment로 병렬 분할된 단권변압기 구조에서 추가로 바깥쪽에 1차 측 병렬 분할이 추가된 레이아웃 구조를 보여준다. 3 GHz의 동작 주파수에서의 최소삽입손실 특성을 고려하여 metal의 폭은  $30~\mu$ m이고, metal 간의 간격은  $10~\mu$ m가 선택되었다. 크기는 그림  $3~\mu$ 에 가지 레이아웃들 모두  $415~\mu$ m×5 $30~\mu$ m이다.

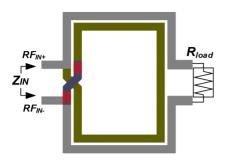

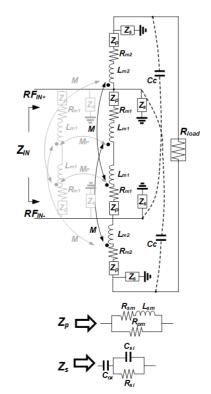

무선통신에 사용 가능한 기가헤르츠 대역까지의 CMOS 공정을 사용한 병렬 분할된 단권변압기에 대한 정확한 성능예측을 위해서는 그림 1의 간단한 형태의 등가회로로 가능하지 않다. 그림 4는 완전한 CMOS 공정 기반 병렬 분할 기법 모델링 구조를 보여준다. 차동구조의 병렬 분할된 단권변압기 구조에 대한 완전한 모델이며, 엷은 회색을 제외한 경우, 1차 측이 1개의 segment로 병렬 분할된 단권변압기에 대한 완전한 모델이며, 엷은 회색이 포함한 경우 1차 측이 2개의 segment로 병렬 분할된 단권변압기에 대한 완전한 모델이며, 엷은 회색이 포함한 경우 1차 측이 2개의 segment로 병렬 분할된 단권변압기에 대한 완전한 모델이다. 기가헤르츠까지의 고주파

그림 4. 제안한 분할된 단권변압기의 완전한 모델

Fig. 4. Proposed complete model of the parallel-segmented autotransformer.

범위까지를 만족시키기 위해 고주파 대역의 특성을 나타 내는  $Z_P$  블록(block)과  $Z_S$  블록이 추가되었다.  $Z_P$  블록의 경우, 표피효과와 근접효과를 반영하기 위해 직렬저항  $R_{sm}$ 과 직렬 인덕터  $L_{sm}$ 과 병렬저항  $R_{sm}$ 의 형태로 구성되 었으며, 1차 측 segment들과 그리고 2차 측 권선마다 추가 되었다. Zs 블록의 경우, lossy한 CMOS substrate의 영향을 반영하기 위해 추가되었다. 1차 측 segment 또는 2차 측 권선과 CMOS substrate의 영향을 반영하기 위해  $Z_s$  블록 은  $C_{or}$ ,  $C_{vi}$ 와  $R_{vi}$ 로 구성되어진다. 또한, 높은 주파수에서 전기적인 상호 간섭을 나타내기 위해 1차 측 segment와 2 차 측 권선 간의 기생 커페시터  $C_c$ 가 추가되었다. 추가적 으로 1차 측 segment들 간의 자기적인 상호결합을 나타내 기 위해  $M_p$ 가 추가되었다. 모델링을 위한 각각의 파라미 터들의 초기 값은 병렬 분할된 점증 단권변압기의 물리 적인 레이아웃을 바탕으로 설정되었으며, 이후 측정결과 와 유사한 경향성을 위해 약간씩 파라미터 값들이 조정 되었다. 병렬 분할된 단권변압기의 1차 측 segment의 수 는 2개 이상으로 가능하다. 제안한 병렬 분할 기법을 활 용한 모델링은 확장성을 가지며, 이 경우, segment를 추가 하여 보다 정확한 성능 예측을 가능하게 한다.

# Ⅲ. 제작된 병렬 분할된 CMOS 점증 단권변압기 측정결과

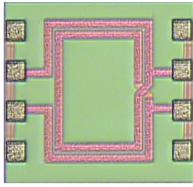

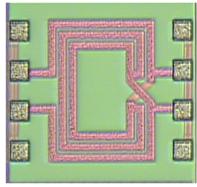

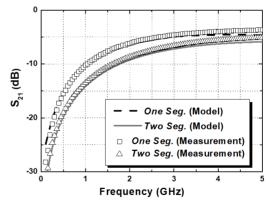

1차 측이 병렬 분할된 점증 단권변압기는 CMOS 65 nm 공정을 통해 제작되었으며, 그림 5는 칩 사진을 나타낸다. 칩의 크기는 1개 그리고 2개의 segment로 병렬 분할된 단권변합기 모두 동일하게 415 μm×530 μm이다. 4 포트 벡터 네트워크 분석기를 이용하여 on-wafer 측정이진행되었다. 4 포트 S 파라미터 측정이진행되었다. 그림 6은 측정된 S<sub>21</sub> 결과와 모델링한 S<sub>21</sub> 결과를 보여준다. 병렬 분할된 점증 단권변압기에 대한 측정결과와 병렬 분할 기법 기반으로 모델링된 곡선은 잘 일치함을 보여준다. 주파수에 따른 측정데이터와 모델링 결과의 root mean square error(RMSE)는 1차 측이 1개/2개의 segment로 병렬 분할된 단권변압기의 경우, 각각 0.6528/0.6462이다. 그림 7은 주파수 변화에 따른 최소삽입손실(minimum insertion loss)에 대한 측정데이터 및 모델링 결과를 보여

- (a) 1개로 병렬 분할된 단권변압기의 칩사진

- (a) Microphotograph of one parallel-segmented autotransformer

- (b) 2개로 병렬 분할된 단권변압기의 칩사진

- (b) Microphotograph of two parallel-segmented autotransformer 그림 5. 병렬 분할된 단권변압기 칩사진

Fig. 5. Microphotographs of parallel-segmented autotransformers.

그림 6. 주파수 변화에 따른  $S_{21}$ 에 대한 측정데이터와 모 델링 결과

Fig. 6. Measured and modeled results of  $S_{21}$  versus frequency.

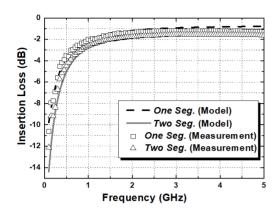

그림 7. 주파수 변화에 따른 최소삽입손실에 대한 측정 데이터와 모델링 결과

Fig. 7. Measured and modeled results of minimum insertion loss versus frequency.

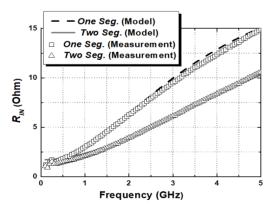

준다. 최소삽입손실은 최대가용이득(maximum available gain)의 역수로 계산되었다 $^{14}$ . 측정된 삽입손실의 경우, 3 GHz에서 1차 측이 1개의 segment로 병렬 분할된 단권 = 변압기의 경우, -1.21 dB, 그리고 1차 측이 2개의 segment로 병렬 분할된 단권변압기의 경우, -1.54 dB 이다. 주파수에 따른 측정데이터와 모델링 결과의 RMSE는 1차 측이 1개/2개의 sement로 병렬 분할된 단권변압기의 경우 각각 0.3218/0.5325이다. 그림 8은 50  $\Omega$  부하에서 변압기를 통해 변환된 변압기 입력 쪽으로 들여다본  $R_{IN}$ 을 보여준다. 측정된  $R_{IN}$ 은 3 GHz에서 1차 측이 1개의 segment로

그림 8. 주파수 변화에 따른  $R_{IN}$ 에 대한 측정데이터와 모델링 결과

Fig. 8. Measured and modeled results of  $R_{IN}$  versus frequency.

표 1. 측정 결과 비교

Table 1. Measurement comparison.

|                                           | Techno-<br>logy | Minimum insertion loss            | $R_{IN}$          | Num-<br>ber of<br>turns | Size                    |

|-------------------------------------------|-----------------|-----------------------------------|-------------------|-------------------------|-------------------------|

| This work One segment autotransformer     | CMOS<br>65 nm   | -1.21 dB<br>@3.0 GHz              | 9.5 Ω<br>@3.0 GHz | 2                       | 0.22<br>mm <sup>2</sup> |

| This work Two segment autotransformer     | CMOS<br>65 nm   | -1.54 dB<br>@3.0 GHz              | 6.1 Ω<br>@3.0 GHz | 3                       | 0.22 mm <sup>2</sup>    |

| Ref. [9]<br>Two segment<br>transformer    | CMOS<br>0.18 μm | -1.52 dB<br>@1.7 GHz              |                   | 4                       | 0.53<br>mm <sup>2</sup> |

| Ref. [8]<br>Reconfigurable<br>transformer | InGaP/<br>GaAs  | -0.96 dB/<br>-0.85 dB<br>@2.4 GHz |                   | 4                       | 0.82<br>mm <sup>2</sup> |

병렬 분할된 단권변압기의 경우, 9.5 \(\Omega\) 그리고 1차 측이 2개의 segment로 병렬 분할된 단권변압기의 경우, 6.1 \(\Omega\) 이다. 주파수에 따른 측정데이터와 모델링 결과의 RMSE 는 1차 측이 1개/2개의 segment로 병렬 분할된 단권변압기의 경우, 각각 0.3371/0.2232이다. 병렬 분할 기법을 활용한 경우, 변압기의 입력 임피던스가 작아져 더 큰 임피던스 변환을 가져와 CMOS 소자로부터 큰 전류의 생성이가능하다.

표 1은 병렬 분할 기법을 사용한 CMOS 이권선 형태의 기존의 일반 변압기와 본 연구에서 제안된 병렬 분할 기법을 사용한 단권변압기의 결과비교이다. 제안된 CMOS 기반 병렬 분할 단권변압기가 이권선 형태의 일반 변압기에 비해 상대적으로 턴 수가 한 개가 작아 변압기 크기를 줄일 수 있어 요구되는 칩 면적을 최소화 할 수 있다.

## Ⅳ. 결 론

본 논문에서는 병렬 분할 점증 단권변압기에서 양호도 Q에 따른 입력 임피던스 변화를 분석하였으며 병렬 분할 기법을 기반으로 확장 가능한 CMOS 점증 단권변압기 모델링 구조를 제안하였다. 제작된 1차 측이 2개의 segment로 병렬 분할된 CMOS 점증 단권변압기는 3 GHz 주파수에서 -1.54 dB의 최소삽입손실의 특성을 보이며, 50  $\Omega$  임피던스를 6.1  $\Omega$ 의 변환을 제공한다. 제안하는 병렬 분

할 단권변압기는 병렬 분할된 이권선을 활용한 일반 변 압기에 비해 상대적으로 턴 수가 적어 작은 면적에 집적 이 가능한 장점이 있다.

#### References

- [1] M. Albulet, *RF Power Amplifiers*. Atlanta, GA, Noble, 2001.

- [2] K. H. An, O. Lee, H. Kim, D. H. Lee, J. Han, and K. S. Yang, et al., "Power-combining transformer techniques for fully-integrated CMOS power amplifiers," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 5, pp. 1064-1075, May 2008.

- [3] O. Lee, J. Han, K. H. An, D. H. Lee, K. S. Lee, and S. Hong, et al., "A charging acceleration technique for highly efficient cascode class-E CMOS power amplifiers, " *IEEE Journal of Solid-State Circuits*, vol. 45, no. 10, pp. 2184-2197, Oct. 2010.

- [4] H. Ahn, S. Back, I. Nam, D. An, J. Lee, and M. Jeong, et al., "A fully integrated —32-dB EVM broadband 802. 11abgn/AC PA with an external PA driver in WLP 40-nm CMOS," *IEEE Transactions on Microwave Theory and Techniques*, vol. 67, no. 5, pp. 1870-1882, May 2019.

- [5] P. Pahl, S. Wagner, H. Massler, A. Leuther, I. Kallfass, and, T. Zwick., "Efficiency optimized distributed transformers for broadband monolithic millimeter-wave integrated power amplifier circuits," *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 12, pp. 4901-4913, Dec. 2017.

- [6] J. R. Long, "On-chip transformer design and application to RF and mm-wave front-ends," in *Proceedings of the* 2017 IEEE Custom Integrated Circuits Conference(CICC), Austin, TX, Apr. 2017, pp. 1-43.

- [7] V. S. Trinh, J. D. Park, "Theory and design of impedance

- matching network utilizing a lossy on-chip transformer," *IEEE Access*, vol. 7, pp. 140980-140989, Sep. 2019.

- [8] D. H. Son, H. Ahn, I. Nam, and O. Lee, "An on-chip low-loss reconfigurable transformer for multimode power amplifiers," *Microwave and Optical Technology Letters*, vol. 61, no. 4, pp. 943-947, Apr. 2019.

- [9] O. Lee, K. H. An, C. H. Lee, and J. Laskar, "A parallel-segmented monolithic step-up transformer," *IEEE Microwave and Wireless Components Letters*, vol. 21, no. 9, pp. 468-470, Sep. 2011.

- [10] V. A. Solomko, P. Weger, "A fully integrated 4.4~ 3.8-GHz power amplifier with autotransformer balun," *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 9, pp. 2160-2172, Sep. 2009.

- [11] H. Ahn, S. Baek, H. Ryu, I. Nam, and O. Lee, "A highly efficient WLAN CMOS PA with two-winding and single-wing combined transformer," in 2016 IEEE Radio Frequency Integrated Circuits Symposium(RFIC), San Francisco, CA, May 2016.

- [12] H. Ahn, S. Baek, I. Nam, D. An, J. K. Lee, and M. Jeong, et al., "A fully integrated dual-mode CMOS power amplifier with an autotransformer-based parallel combining transformer," *IEEE Microwave and Wireless Components Letters*, vol. 27, no. 9, pp. 833-835, Sep. 2017.

- [13] H. Ahn, S. E. Choi, H. Ryu, S. Baek, I. Nam, and O. Lee, "2.3-GHz HBT power amplifier with parallel-segmented on-chip autotransformer," *IEEE Microwave and Wireless Components Letters*, vol. 27, no. 12, pp. 1140-1142, Oct. 2017.

- [14] O. El-Charniti, E. Kerhervé, and J. B. Bégueret, "Modeling and characterization of on-chip transformers for silicon RFIC," *IEEE Transactions on Microwave Theory and Techniques*, vol. 55, no. 4, pp. 607-615, Apr. 2007.

## 안 현 진 [부산대학교/석·박사통합과정]

#### https://orcid.org/0000-0002-3859-2473

2015년 2월: 부산대학교 전기전자공학부 (공학사)

2015년 3월~현재: 부산대학교 전기컴퓨 터공학과 박사과정

[주 관심분야] RF IC, 디지털 송신기, RF Power Amplifier, HBT·CMOS 집적회로 등

### 류 현 식 [RFHIC/연구원]

#### https://orcid.org/0000-0002-8911-7461

2013년 2월: 신라대학교 전자공학과 (공학 사)

2015년 8월: 부산대학교 전자전기컴퓨터 공학과 (공학석사)

2018년~2019년 12월: RFcore 연구원 2019년 12월~현재: RFHIC mmic 연구원 [주 관심분야] 초고주파 회로 설계, RF

Power Amplifier, CMOS 집적회로 등

## 손 병 찬 [부산대학교/학생]

#### https://orcid.org/0000-0001-8375-637X

2020년 2월: 부산대학교 전기공학과 (공학 사)

[주 관심분야] RF Power Amplifier, CMOS 집적회로 등

## 이 옥 구 [부산대학교/교수]

#### https://orcid.org/0000-0001-8244-5115

2001년 2월: 성균관대학교 전기전자 및 컴 퓨터공학부 (공학사)

2005년 2월: 한국과학기술원 전기 및 전자 공학과 (공학석사)

2009년 12월: Georgia Institute of Technology 전기 및 전자공학과 (공학박사)

2010년 1월~2012년 8월: Qualcomm Inc.,

Qualcomm CDMA Technologies, Senior Engineer 2012년 9월~현재: 부산대학교 전기공학과 부교수 [주 관심분야] CMOS 송수신단 집적회로, 전력증폭기, 바이오 메디컬 회로 및 시스템