# 전류 피크를 낮춘 SSPA 펄스변조 바이어스 회로 설계

# Pulse Modulator Bias Circuit Design of Solid-State Power Amplifier for Low Peak Current

김석권·김성완·이성세·황환성\*·김효종\*

Seokkwon Kim · Sung-Wan Kim · Sung-Sae Lee · Hwan Seong Hwang\* · Hyo Jong Kim\*

유 약

본 논문에서는 SSPA(Solid-State Power Amplifier) 드레인의 펄스변조 바이어스 회로에서 커패시터 뱅크 충전으로 인한 전류 피크를 경감하는 것을 고려하였다. 펄스변조 바이어스 회로에서 전압 레귤레이터와 커패시터 뱅크 사이에 인덕터를 추가하면 충전 시간을 지연하여 전류 피크를 낮출 수 있으며, 인덕터의 용량과 DCR(DC Resistance)에 따른 전류 충전 특성을 댐핑 시정수와 오실레이션 주파수로 분석하였다. 최대 PRF(Pulse Repetition Frequency) 2,600 Hz를 고려하여 주기내에 충전이 되도록 시정수와 오실레이션 주파수의 적절 범위를 제안하였다. 회로 모의 시험을 통해 인덕터의 충전 지연을 통해 전류 피크가 상당히 감소되며, 전류 충전 특성은 분석 결과와 유사함을 확인하였다. 대기 전류를 제외한 전류 피크와 평균의 비는 인덕터가 없는 시제품의 경우 10.0 A/A이었으며, 인덕터가 적용된 시제품은 2.3 A/A로 개선되며, 충전 지연이 적절함을 확인하였다.

#### **Abstract**

This paper investigates pulse modulator bias circuit design for the drain of solid-state power amplifier with low peak charging current of capacitor banks. By using an inductor between a voltage regulator and the capacitor banks in the pulse modulator bias circuit, the charging time is delayed and current peak is reduced. The current charging characteristics corresponding to the inductance and DC resistance of the inductor are analyzed based on the damping time constant and oscillation frequency. Bounds of damping time constant and oscillation frequency are set for the capacitor banks to be charged by specified time periods for a maximum pulse repetition frequency of 2,600 Hz. Simulation results show that the current peak is significantly reduced by the inductor, and the current charging characteristics are similar to the analysis. The ratio of current peak and mean excluding stand-by current of a prototype without inductor is 10.0 A/A, while that of a prototype with inductors is enhanced to 2.3 A/A with an appropriate charging delay.

Key words: SSPA, Pulse Modulator Bias Circuit, Peak Current

Ⅰ. 서 론

누리호(한국형발사체, KSLV-II, Korea Space Launch Vehicle-II) 최상단에는 C-밴드 트랜스폰더(transponder)와

<sup>「</sup>이 연구는 과학기술정보통신부에서 시행한 한국형발사체개발사업의 연구비 지원으로 연구되었음.」

한국항공우주연구원(Korea Aerospace Research Institute)

<sup>\*</sup>단암시스템즈(Danam Systems)

<sup>·</sup> Manuscript received June 5, 2019; Revised July 4, 2019; Accepted August 13, 2019. (ID No. 20190605-057)

<sup>·</sup> Corresponding Author: Seokkwon Kim (e-mail: seokkwon@kari.re.kr)

C-밴드 안테나가 탑재되며, 지상 레이다의 발사체 위치 추적에 활용된다. 트랜스폰더는 레이다에서 송신한 질의 펄스(interrogation pulse) 신호를 수신하고, 이에 따른 응답 펄스(reply pulse)를 지상으로 송신한다.

트랜스폰더의 송신부는 SSPA(Solid-State Power Amplifier)를 이용하여 RF(Radio Frequency) 응답펄스를 증폭한다. SSPA 방식은 마그네트론을 이용한 증폭방식에 비해 안정적이고, 저전압 구동이 가능하며, 기밀 유지의 필요성이 없는 등 장점이 있다. 트랜스폰더 송신 펄스의 피크전력 규격은 듀얼 포트 각각 50 dBm 이상, 펄스폭( $t_{PW}$ )은 정격 500 ns, 펄스의 상승시간(rising time) 및 하강시간(falling time) 등의 규격은 IRIG(Inter-Range Instrumentation Group) 262-02 표준을 따르며 표 1과 같다[1]. PRF(Pulse Repetition Frequency,  $f_{PR}$ )는 최대 2,600 Hz 이내에서 가변적이며, 이에 따른 송신 펄스의 듀티비(duty ratio)는 최대 0.13 % 이내이다.

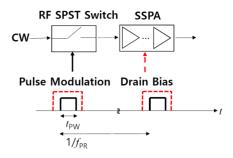

트랜스폰더의 송신부는 주파수합성기(frequency synthesizer), RF SPST(Single Pole Single Throw) 스위치 및 다단의 SSPA 등으로 구성된다. 주파수합성기는 5 GHz 대역의 CW(Continuous Wave) 송신 주파수 신호원이며, FPGA(Field Programmable Gate Array)는 응답펄스의 트리거링에 따라 RF SPST 스위치를 500 ns 동안 On하여 펄스로 진폭변조 (amplitude modulation: AM)한다. FPGA가 RF 스위치의 On/Off 시점에 따라 SSPA의 드레인 바이어스 전원을 제어하는 펄스변조 바이어스 회로가 있으며, 스위치의 On/Off 시점 전후로 일정한 여유를 두고 전원공급을 하여 신호가안정적으로 증폭되도록 한다<sup>[2]~[6]</sup>. SSPA의 게이트 바이어스 전원은 연속적으로 공급한다. 그림 1은 RF 스위치 제어와 SSPA의 바이어스 제어를 도식적으로 나타낸 것이다. 펄스 모드로 동작하는 SSPA의 전류 소모는 RF 증폭 구

표 1. 송신 펄스의 주요 규격 Table 1. Specifications of Tx pulse.

| Parameter    | Specification |  |

|--------------|---------------|--|

| Pulse width  | 500±100 ns    |  |

| Rising time  | ≤ 100 ns      |  |

| Falling time | ≤ 150 ns      |  |

| PRF          | 10∼2,600 Hz   |  |

그림 1. RF 펄스변조 및 SSPA 드레인 바이어스 스위칭 Fig. 1. RF pulse modulation and switching of SSPA drain bias.

간에서는 크지만, 듀티비를 고려한 평균은 작은 것이 특징이다. 일반적으로 펄스변조 전원회로는 참고문헌 [4], [6], [7]과 같이 커패시터 뱅크(capacitor bank)를 이용하여 SSPA에 순간적인 전류를 공급하며, 커패시터 뱅크는 바이어스 제어에 따라 방전 및 충전된다.

커패시터 뱅크의 충전으로 인한 전류 피크가 크면 전원 부 소자의 전류 정격을 높이거나 구성이 복잡해질 수 있으 며, 발사체 탑재 환경에서 전원버스에 연결된 다른 장치에 영향을 줄 수 있어 바람직하지 않다. 본 논문의 2장에서는 커패시터 뱅크의 충전 전류 피크를 낮추기 위한 펄스변조 바이어스 회로 구성 및 분석을 살펴보고, 3장에서는 이에 대한 모의 시험 결과를 제시하였다. 4장에서는 시제품의 전류 피크 측정 결과를 확인하였다.

#### Ⅱ. SSPA 펄스변조 바이어스 회로

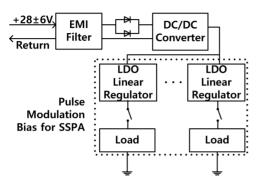

트랜스폰더의 전원부는 그림 2와 같이 전원분배장치에서 28±6 V의 전원을 공급받으며, DC/DC 컨버터의 스위칭잡음을 억제하기 위한 EMI(Electromagnetic Interference) 필터, 역전압 보호를 위한 다이오드, 절연형(isolation) DC/DC 컨버터 등으로 구성된다. SSPA의 드레인 전원은 DC/DC 컨버터에 연결된 LDO(Low Drop-Out) 선형(linear) 전압 레귤레이터를 이용한다. SSPA의 다단 구성에 따라 레귤레이터를 포함한 펄스변조 바이어스 회로는 복수로 구성되었다. 그림 2는 트랜스폰더 전원부에서 SSPA의 드레인 바이어스와 관련된 부분을 나타낸 것이며, 추가적으로 수신부의 전원 공급을 위한 DC/DC 컨버터와 레귤레이터 등이

그림 2. 트랜스폰더 전원부의 SSPA 펄스변조 바이어스 블록다이어그램

Fig. 2. Block diagram for power supply circuit of the transponder related with pulse modulation bias of SSPA.

있다.

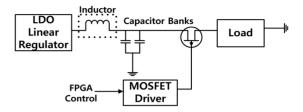

그림 3은 펄스변조 바이어스 회로의 블록다이어그램이며, MOSFET(Metal Oxide Field Effect Transistor) 드라이버는 MOSFET 게이트의 커패시턴스 충전에 필요한 전류를 빠르게 공급함으로써 MOSFET이 고속으로 스위칭되도록한다. MOSFET이 도통되면 커패시터 뱅크는 방전되어 SSPA 드레인에 전원을 공급하며, 방전된 전하량은 다음과같이 나타낼 수 있다.

$$\Delta Q = \int i_{DS} dt \tag{1}$$

여기에서  $i_{DS}$ 는 SSPA의 드레인 전류이다. 방전으로 인한 커패시터 뱅크의 전압 하강은 다음과 같다.

$$\Delta V = \Delta Q / C_B \tag{2}$$

여기에서  $C_B$ 는 커패시터 뱅크의 용량이다. 예를 들어  $1 \mu s$  동안 바이어스를 걸어줄 때  $i_{DS}$ 가 20 A로 일정하다면,  $C_B$ =300  $\mu F$ 일 때  $\Delta V$ 는  $66.7 \, \mathrm{mV}$ 로 산출된다. 단,  $i_{DS}$ 는 RF 스위치  $\mathrm{On/Off}$  및 바이어스 전압 변화에 따라 변동될 수 있으며 단순화를 위해 이와 같이 산출하였다.

그림 3은 참고문헌 [4], [6], [7]의 기존 회로와는 다르게 커패시터 뱅크의 충전 시 발생하는 전류 피크를 억제하기 위한 인덕터가 추가되었으며, 레귤레이터와 커패시터 뱅크 사이에 위치한다. 인덕터의 용량을 L, 이것의 DCR(DC Resistance)을  $R_{DCR}$ , 커패시터 뱅크의  $ESR(Equivalent Series Resistance)을 <math>R_{FSR}$ 이라 하였을 때 전류는 다음과 같이 표현

그림 3. SSPA 펄스변조 바이어스 회로

Fig. 3. Pulse modulation bias circuit for SSPA.

할 수 있다.

$$L\frac{di}{dt} + (\underbrace{R_{DCR} + R_{ESR}}_{=R})i + \frac{1}{C_B} \int idt + V_{C_B} = V_S(t)$$

(3)

여기에서  $V_{C_s}$ 는 커패시터 뱅크가 방전 후 잔존하는 전압이며,  $V_S(t)$ 는 레귤레이터의 출력 전압이다. 레귤레이터는 전압 제어 피드백에 따라  $V_S(t)$ 가 정격 출력 전압으로복귀하도록 전류를 공급할 것이다. 위 식은 전형적인 RLC회로에 관한 것이지만,  $V_S(t)$ 는 레귤레이터의 특성을 따른다.

인덕터에 따른 전류 특성을 분석하기 위하여  $V_S(t)$ 를 정격 출력 전압인 상수로 근사화하면, 식 (3)은 이차 미분 방정식의 특성에 따라 임계댐핑(critical damping), 오버댐 핑(overdamping) 및 언더댐핑(underdamping)인 경우로 나뉜다<sup>[5]</sup>. 첫 번째  $L=\frac{R^2C_B}{4}$ 인 조건에서 전류는 임계댐핑되며, 다음과 같이 나타낼 수 있다.

$$i(t) = (c_1 + c_2 t) \cdot e^{-t/\tau}, \text{ where } \tau = \left(\frac{R}{2L}\right)^{-1}.$$

(4)

여기에서  $c_1$ 과  $c_2$ 는 초기 조건에 의해 결정되는 계수(coefficients)이고,  $\tau$ 는 댐핑의 시정수(time constant)로서  $t=3\tau$ 가 되는 시점에서 전류는 상당 부분 수렴할 것이다. 펄스의 최소 주기인 384.6  $\mu$ s(최대 PRF 2,600 Hz) 내에 커패시터 뱅크의 충전이 대부분 이루어지기 위하여  $3\tau < 384.6$   $\mu$ s가 되는 것이 바람직할 것이다. 시정수  $\tau$ 의 감소를 위해 인덕터의 용량을 줄일 수 있지만, 이에 따른 DCR 또한감소되어 원치 않는 결과를 얻을 수 있으므로 유의해야한다.

두 번째  $L < \frac{R^2 C_B}{4}$ 인 조건에서 전류는 오버댐핑되며,

두 시정수는 다음과 같이 나타낼 수 있다.

$$\begin{split} \tau_1 &= \left(\frac{R}{2L} - \sqrt{\left(\frac{R}{2L}\right)^2 - \frac{1}{LC_B}}\right)^{-1} \\ \tau_2 &= \left(\frac{R}{2L} + \sqrt{\left(\frac{R}{2L}\right)^2 - \frac{1}{LC_B}}\right)^{-1} \end{split} \tag{5}$$

$au_1 > au$ 이고 전류의 수렴 시간은 시정수가 큰 값에 의존하므로  $3 au_1 < 384.6~\mu$ s이 바람직할 것이다. 마지막으로  $L > rac{R^2 C_B}{4}$ 인 조건에서 전류는 언더댐핑되어 전류가 최초로 0으로 수렴하는 시간은 임계댐핑인 경우보다 짧아지지만, 오실레이션으로 전류 소모가 증가할 수 있다. 시정수는 식 (4)의 au와 같으며, 오실레이션의 주파수 성분  $f_d$ 는 다음과 같다.

$$f_d = \frac{\omega_d}{2\pi} = \frac{1}{2\pi} \left( \sqrt{\left| \left( \frac{R}{2L} \right)^2 - \frac{1}{LC_B} \right|} \right) \tag{6}$$

댐핑 과정에서 오실레이션의 영향이 크지 않도록  $f_d < \frac{1}{2} \cdot \frac{1}{3\tau}$ 이 만족되면 바람직할 것이다.

회로 구동에서 레귤레이터의 출력 전압  $V_s(t)$ 는 피드백 제어에 따라 정격 출력 전압으로 수렴할 것이고, 레귤레이터의 정격 최대 전류, 제어 특성 등으로 인하여 댐핑조건 및 수렴시간에 대한 결과는 분석과 차이가 있을 수있다. 시정수 및 오실레이션 주파수에 관한 조건은 반드시준수되어야 하는 사항은 아니며, 설계 시 권고 사항으로활용하면 될 것이다.

#### Ⅲ. 모의 시험 결과

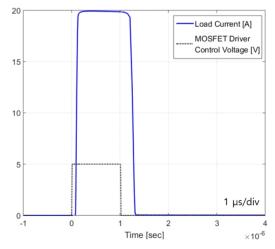

Orcad Pspice를 이용한 회로 시뮬레이션에서 그림 3의 레귤레이터 입력단은 이상적인 +12~V 전원 소스이고, 이 것의 출력 전압은 정격 +10~V로 모델링하였다. 바이어스 회로의 부하단은 부하 전류를 바탕으로 저항으로 모사하였다. 시뮬레이션에서  $I_{DS}\approx 20~A$ , MOSFET 드라이버 제어 신호의 On 시간  $1~\mu$ s, 이것의 상승시간  $t_R=10~{\rm ns}$ , 이것의 하강시간  $t_F=10~{\rm ns}$ ,  $C_B=300~\mu$ F,  $R_{ESR}=10~{\rm m}\Omega$  으로 설정하였다. 인덕터는 표 2와 같이 다섯 가지 경우를 고려하였다.

표 2. 시뮬레이션에서 인덕터의 용량과  $R_{DCR}$  설정 Table 2. Inductance and  $R_{DCR}$  of inductors in simulation.

| # | $L  [ \mu  { m H}]$ | $R_{DCR}$ [m $\Omega$ ] | Damping         | Coefficients                              |

|---|---------------------|-------------------------|-----------------|-------------------------------------------|

| 1 | 10                  | 160                     | Under damping   | $	au$ =118 $\mu$ s $f_d$ =2,572 Hz        |

| 2 | 22                  | 370                     | "               | $	au$ =116 $\mu$ s $f_d$ =1,396 Hz        |

| 3 | 33                  | 510                     | "               | $	au$ =127 $\mu$ s $f_d$ =993 Hz          |

| 4 | 68                  | 860                     | "               | $	au$ =156 $\mu$ s $f_d$ =453 Hz          |

| 5 | 100                 | 1270                    | Over<br>damping | $	au_1$ =275 $\mu$ s $	au_2$ =109 $\mu$ s |

1번부터 4번까지는 언더댐핑인 조건이고 5번은 오버댐핑인 조건이다. 각각의 시정수와 오실레이션 주파수는 식(4)~(6)에 따라 나타내었으며, 2번과 3번의 시정수와 오실레이션 주파수는 설계 기준 조건을 만족하는 경우이다.

커패시터 뱅크가 완충된 상태에서 방전 및 충전 특성을 관찰하기 위하여 펄스변조 바이어스를 1회 On/Off 한 경우를 모의하였다. 부하의 전류 및 전압 특성은 그림 4와 같으며, X축 시간 단위는  $1~\mu$ s이다. MOSFET 드라이버 제어 신호의 On 시간은  $t=0\sim1~\mu$ s이지만, 부하에 전류가 공급된 시간은 드라이버의 지연 및 MOSFET 게이트의 커

그림 4. 부하 전류 및 MOSFET 드라이버 제어전압 모델링 Fig. 4. Load current and MOSFET driver control voltage.

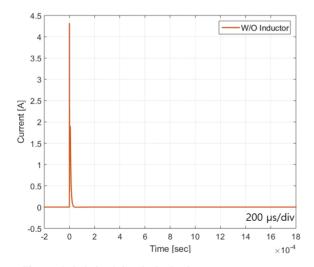

패시턴스 성분 등으로 인하여 이보다 크게 모델링되었다. 인덕터가 없는 경우, 커패시터 뱅크의 충전 전류는 그림 5와 같으며, 이것은 레귤레이터의 입력 전류이다. 그림 5에서 X 축의 단위는  $200~\mu$ s이다. 충전 초기에 4~A 이상의 전류 피크가 관찰되며, 이후 전류는 레귤레이터의 단락 조건에서의 최대 전류 모델링에 따라 약 2~A로 제한되는 특성을 보인 후 빠른 속도로 수렴한다.

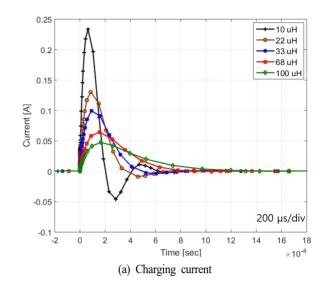

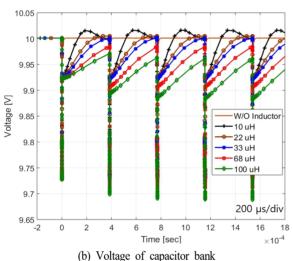

표 2의 인덕터에 따른 커패시터 뱅크의 충전 전류 특성은 그림 6(a)와 같으며, 인덕터가 없는 그림 5에 비하여 전류 피크가 크게 낮아짐을 확인할 수 있다. 또한, 인덕터용량이 커짐에 따라 전류 피크는 낮아지지만 수렴시간은 DCR의 영향으로 일정한 경향성을 보이지 않았다. L=10  $\mu$ H일 때에는  $f_d$ 가 커서 오실레이션 경향이 크게 나타났지만, L=22  $\mu$ H, 33  $\mu$ H, 68  $\mu$ H인 경우에는 오실레이션이미비하였다. 이러한 오실레이션 특성은 표 2의  $f_d$  분석 결과와 유사하였다. L=22  $\mu$ H, 23  $\mu$ H인 경우, 230 240 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250 250

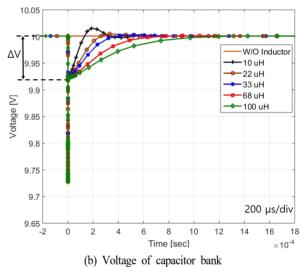

그림 6의 (b)는 충전에 따른 커패시터 뱅크의 전압을 나타내었다. 그림 4에서 바이어스 구간이 1  $\mu$ s보다 크게 모델링되어 커패시터 뱅크의 방전으로 인한 전압 강하  $\Delta V$ 는 식 (1)에서 산출한 66.7 mV에 비해 다소 큰 것을 알

그림 5. 인덕터가 없을 때 충전 전류 Fig. 5. Charging current without inductor.

그림 6. 인덕터에 따른 충전 전류와 커패시터 뱅크의 전압 Fig. 6. Charging current and voltage of capacitor bank corresponding to inductors.

수 있다. 인덕터가 없는 경우, +10 V로의 전압 회복은 매우 빠르게 됨을 알 수 있다.

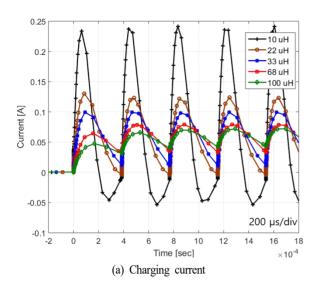

최대 PRF인 2,600 Hz에서 커패시터 뱅크의 방전이 이뤄질 때 인덕터에 따른 커패시터 뱅크의 충전 특성은 그림 7과 같다. 시정수가 큰  $L=68~\mu\mathrm{H}$ ,  $100~\mu\mathrm{H}$ 인 경우에는 수렴 시간이 길어 커패시터 뱅크의 충전 전압이  $+10~\mathrm{V}$ 보다 작은 것을 알 수 있다. 이러한 경우, 시간이 지남에 따라 SSPA의 바이어스 전압이 하강할 수 있으며, RF 출력 특성

그림 7. PRF 2,600 Hz일 때 인덕터에 따른 충전 전류와 커패시터 뱅크의 전압

Fig. 7. Charging current and voltage of capacitor bank corresponding to inductors for PRF 2,600 Hz.

에 영향을 줄 수 있다. 그림 6과 그림 7을 통하여 L=22  $\mu$ H, 33  $\mu$ H인 경우 오실레이션 및 수렴 특성이 양호한 것을 알 수 있다.

#### Ⅳ. 시제품 전류 측정 결과

트랜스폰더의 시제품(prototype) 1의 펄스변조 바이어스 회로에는 레귤레이터와 커페시터 뱃크 사이에 인덕터가 없으며, 시제품 2에서는 표 2의 33  $\mu$ H 인덕터가 적용되었다. 33  $\mu$ H 인덕터는 22  $\mu$ H 인덕터에 비해 전류 피크가 낮을 것으로 예상된다. 전류는 전류 프로브(current probe)와 오실로스코프를 이용하여 그림 2의 외부 전원 입력단에서 측정하였으며, 외부 전원은 +28 V로 설정하였다. 전류 측정 결과에는 EMI 필터, DC/DC 컨버터 등의 특성과트랜스폰더의 대기(stand-by) 상태에서의 전류가 반영되며, SSPA의 다단 구성에 따라 바이어스 회로가 복수로 구성되어 3장의 모의 시험결과와 차이가 있을 수 있다. 비록시제품 1과 시제품 2는 SSPA 구성, DC/DC 컨버터, EMI 필터 구성 등에서 다소 다른 부분이 있지만, 인덕터 유무에 따른 전류 피크의 경향은 확인할 수 있다.

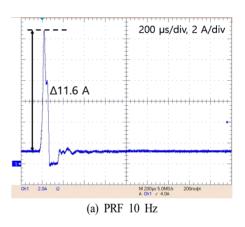

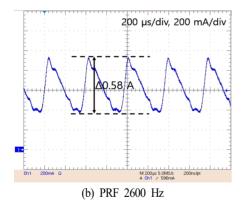

인덕터가 적용되지 않는 시제품 1의 대기전류  $I_s$ 는 1.2 A이고, 전류 측정 결과는 그림 8과 같다. PRF 10 Hz일 때

그림 8. 인덕터가 없는 시제품 1의 전류 측정 결과

Fig. 8. Current measurement results of prototype 1 without inductor.

전류 피크  $I_p$ 는 12.8 A이고, 피크와 대기 전류와의 차이  $\Delta I_p$ 는 다음과 같이 표현되며 11.6 A이다.

$$\Delta I_p = I_p - I_s \tag{7}$$

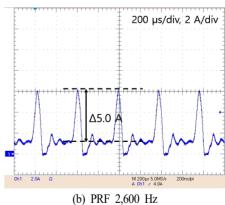

PRF 2,600 Hz일 때  $I_p$ 는 6.2 A,  $\triangle I_p$ 는 5.0 A, 평균  $I_m$ 은 1.7 A이고, 평균과 대기 전류와의 차이  $\triangle I_m$ 은 다음과 같이 나타내며 0.5 A이다.

$$\Delta I_m = I_m - I_s \tag{8}$$

대기 전류를 제외한 전류 피크와 평균의 비는  $\triangle I_n$ 와  $\triangle I_m$ 의 비로 나타낼 수 있으며, PRF 2,600 Hz에서 시제품 1은 10.0 A/A로 산출된다.

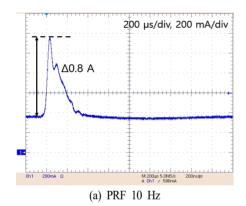

그림 9는 33  $\mu$ H 인덕터가 적용된 시제품 2의 전류 측정 결과이며, 시제품 2의 대기전류는 0.36 A이다. PRF 10 Hz일 때  $I_{\mu}$ 는 1.16 A이고,  $\Delta I_{\mu}$ 는 0.8 A이다. PRF 2,600 Hz일 때

그림 9. 33  $\mu$ H 인덕터가 적용된 시제품 2의 전류 측정 결과 Fig. 9. Current measurement results of prototype 2 with 33  $\mu$ H inductors.

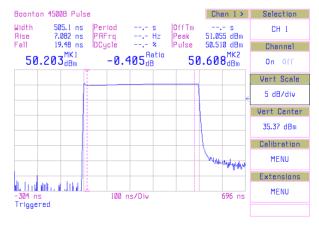

$I_p$ 는 0.94 A,  $I_m$ 은 0.61 A이며,  $\triangle I_p$ =0.58 A,  $\triangle I_m$ =0.25 A,  $\triangle I_p$ / $\triangle I_m$ =2.3 A/A이다. 시제품 2의 수렴 시간과 오실레이션 특성은 양호하였으며, RF 펄스 측정 결과는 그림 10과 같이 표 1의 펄스의 펄스폭, 상승 및 하강 시간 등의규격을 만족하는 것을 알 수 있다. 참고로, 시제품 1과 시제품 2의 RF 펄스폭, 상승 및 하강 시간 등의 측정결과는유사하다. 단, 시제품 1의 RF 펄스 전력은 전력 모니터를위한 커플링 손실로 인하여 약 48 dBm이다.

PRF 2,600 Hz에서 시제품 1과 2의 전류 특성은 표 3에 나타내었다.  $\Delta I_m$ 은 SSPA 구동으로 인한 전류의 평균이며, 두 시제품은 SSPA 구성에서 다소 차이가 있어 전류 피크를 직접적으로 비교하기는 어렵다. 전류 피크의 개선은  $\Delta I_m$ 의 상대적인 비로 비교할 수 있으며, 시제

표 3. PRF 2,600 Hz에서 시제품 1과 2의 전류 특성 Table 3. Current characteristic of prototypel and 2 for PRF 2,600 Hz.

|                               | Prototype 1 | Prototype 2 |

|-------------------------------|-------------|-------------|

| $I_{s}$ [A]                   | 1.2         | 0.36        |

| $I_p$ [A]                     | 6.2         | 0.94        |

| $I_m$ [A]                     | 1.7         | 0.61        |

| $\Delta I_p$ [A]              | 5.0         | 0.58        |

| $\Delta I_m$ [A]              | 0.5         | 0.25        |

| $\Delta I_p/\Delta I_m$ [A/A] | 10.0        | 2.3         |

그림 10. 시제품 2의 RF 펄스 측정결과

Fig. 10. RF pulse measurement result of prototype 2.

품 1은 10.0 A/A에서 시제품 2는 2.3 A/A로 상당히 개선됨 을 알 수 있다.

#### Ⅴ. 결 론

본 논문에서는 SSPA 펄스변조 바이어스 회로에서 인덕 터의 충전 지연을 이용하여 전류 피크를 낮추는 것을 살펴 보았다. 커패시터 뱅크의 용량과 ESR, 인덕터의 용량과 DCR에 따른 충전 전류의 댐핑 시정수와 오실레이션 주파 수를 분석하였으며, 최대 PRF 2,600 Hz를 고려하여 이것 의 적절한 범위를 제안하였다. 모의 시험을 통해 인덕터 유무에 따른 전류 피크의 차이를 확인하였으며, 인덕터에 따른 충전 전류의 댐핑과 오실레이션 특성은 분석 결과와 유사하였다. 인덕터가 없어 전류 피크가 큰 시제품 1과 인 덕터를 적용하여 전류 피크를 낮춘 시제품 2의 측정 결과 를 비교하였으며, 본 논문에서 제안하는 기법이 효과적임 을 확인하였다.

#### References

- [1] C(G)-band & X(I)-band Noncoherent Radar Transponder Performance Specification Standard, IRIG Standard 262-02, 2002.

- [2] H. M. Yi, S. Y. Hong, "Design of high speed switching circuit for pulsed power amplifier," *The Journal of Ko*rean Institute of Electromagnetic Engineering and Science, vol. 19, no. 2, pp. 174-180, Feb. 2008.

#### 김 석 권 [한국항공우주연구원/선임연구원]

https://orcid.org/0000-0001-6215-8709

2005년 8월: 한양대학교 전자전기컴퓨터공 학부 (공학사)

2008년 2월: 한국과학기술원 전기및전자공 학과 (공학석사)

2011년 8월: 한국과학기술원 전기및전자공 학과 (공학박사)

2011년 9월~현재: 한국항공우주연구원

선임연구원

[주 관심분야] Launch Vehicle On-Board RF Systems, Signal Processing in Communication Systems 등

- [3] J. Dhar, S. K. Garg, R. K. Arora, B. V. Bakori, and S. S. Rana, "Spaceborne C-band pulsed solid state power amplifier," in 2009 Applied Electromagnetics Conference (AEMC), Kolkata, 2009, pp. 1-4.

- [4] H. J. Kim, M. H. Yoon, P. S. Chang, W. S. Kim, and J. W. Lee, "Design and fabrication of X-band 50 W pulsed SSPA using pulse modulation and power supply switching method," *The Journal of Korean Institute of Electromagnetic Engineering and Science*, vol. 22, no. 4, pp. 440-446, Apr. 2011.

- [5] S. K. Giri, S. K. Shome, and A. K. Ball, "Design of C-band high speed pulsed power amplifier for pulsed radar applications," *International Journal of Electronics* and Electrical Engineering, vol. 1, no. 2, pp. 61-65, Jun. 2013.

- [6] H. J. Kim, J. W. Lee, "Design of a low-power RF transceiver for small UAVs using switching power," *The Journal of Korean Institute of Electromagnetic Engineering and Science*, vol. 28, no. 10, pp. 779-787, Oct. 2017.

- [7] A. Tripathi, M. K. Badapanda, R. Upadhyay, and M. Lad, "Design and development of 50 V, 300 A pulse power supply for solid state RF amplifiers," in *Proceedings of the 7th DAE-BRNS Indian Particle Accelerator Conference*, India, Dec. 2015.

- [8] E. Kreyszig, Advanced Engineering Mathematics, 8th ed. New York, NY, John Wiley & Sons, pp. 72-90, 1999.

# 김 성 완 [한국항공우주연구원/책임연구원]

https://orcid.org/0000-0002-4895-7173

1998년 2월: 충남대학교 전자공학과 (공학 사)

2000년 2월: 충남대학교 전파공학과 (공학 석사)

2017년 2월: 충남대학교 전파공학과 (공학 박사)

2000년 3월~2001년 3월: 한국전자통신연

구원 연구원

2001년 4월~현재: 한국항공우주연구원 책임연구원 [주 관심분야] 안테나, 초고주파 회로 및 시스템, 레이다

# 이 성 세 [한국항공우주연구원/선임연구원]

#### https://orcid.org/0000-0002-5016-8130

2001년 2월: 경북대학교 전기/전자공학부 (공학사)

2003년 2월: 한국과학기술원 전기/전자공 학부 (공학석사)

2007년 2월: 한국과학기술원 전기/전자공 학부 (공학박사)

2007년 2월~2007년 12월: 페어차일드코

리아 반도체

2007년 12월~현재: 한국항공우주연구원 선임연구원 [주 관심분야] 전력전자, 배터리

# 김 효 종 [단암시스템즈/수석연구원]

#### https://orcid.org/0000-0001-9118-6805

1997년 2월: 경희대학교 전파공학과 (공학 사)

1999년 2월: 경희대학교 전파공학과 (공학 석사)

2018년 2월: 경희대학교 전파공학과 (공학 박사)

1999년 1월~현재: 단암시스템즈 수석연

구원

[주 관심분야] 초고주파 회로 및 시스템, 주파수 합성

## 황 환 성 [단암시스템즈/수석연구원]

## https://orcid.org/0000-0002-6758-3234

2002년 2월: 광운대학교 전파공학과 (공학 사)

2007년 2월: 광운대학교 이동및무선통신 과 (공학석사)

2011년 12월~현재: 단암시스템즈 수석연 구위

[주 관심분야] 초고주파 회로 및 시스템,

송수신기, SSPA, 레이다 등