# 초고속 이동체 탐지에 적합한 초광대역 CMOS RFIC 기반 레이다 시스템

# A CMOS UWB RFIC Based Radar System for High Speed Target Detection

김 상 균 · 어 윤 성 · 박 형 철\*

Sang Gyun Kim · Yun Seong Eo · Hyung Chul Park\*

요 약

본 논문에서는 초고속 이동체 탐지에 적합한 상보형 금속산화 반도체(CMOS) 초광대역(UWB) RFIC 기반의 레이다 시스템을 제안한다. 시스템의 거리 분해능은 15 cm이고, 탐지 범위는 15 m에 이른다. 시스템 구현을 위해서 단일 칩 CMOS UWB IC를 설계, 구현한다. 포락선 검출과 등가 시간 샘플링 구조를 이용하여 측정 및 신호처리 시간을 대폭 단축한다. 측정을 통해서 UWB 펄스의 대역폭은 0.5~1.0 GHz이며, 중심주파수는 3.5~4.5 GHz 임을 보인다. 또한 15 m 범위의 신호 수신을 포함하여 대상체 거리값 출력까지의 신호처리 시간은 150 μsec임을 보인다.

### Abstract

This paper presents CMOS UWB RFIC based radar system for high speed target detection. The system can achieve resolution of 15 cm and detection range of 15 m. For developed system, single chip CMOS UWB IC is implemented. To reduce the measuring and processing time, envelope detection and equivalent time sampling technique are used. Measurement results show that the bandwidth and center frequency of UWB pulse can be adjusted in the range of  $0.5 \text{ GHz} \sim 1.0 \text{ GHz}$ ,  $3.5 \text{ GHz} \sim 4.5 \text{ GHz}$ , respectively. Signal processing time including scan time over 15 m distance is about  $150 \mu \text{ sec}$ .

Key words: UWB, RFIC, Radar, High Speed, Mismatch

# T. 서 론

초광대역(UWB: Ultra Wide-Band) 레이다(radar)는 거리 분해능이 매우 정밀하여 상업용 및 군사용 근거리 레이 다로서 활발한 연구가 진행되고 있다. UWB 레이다는 송 신 전력이 낮아 탐지 범위는 짧지만 분해능은 주파수변 조(FMCW: Frequency Modulation Continuous Wave) 레이 다 등에 비해서 정밀한 장점이 있다. 최근에는 사람의 탐지, 의료영상 등의 분야를 위한 고집적 상보형 금속산화반도체(CMOS) UWB 레이다 IC 및 system에 대한 논문들이 발표되었다<sup>[1]~[4]</sup>. UWB 레이다가 수 cm 또는 1 cm 이하의 정밀한 분해능을 갖기 위해서는 수-GHz 이상의 초고속 샘플링 기술이 필요하다. 그래서, 대부분의 UWB 레이다는 등가 시간 샘플링(equivalent time sampling), 시간

<sup>「</sup>이 연구는 한국산업기술평가관리원을 통해 산업통상자원부의 산업기술혁신사업(10053023, IoT향 다중대역 RF MEMS 소자 원천기술 개발) 및 서울 과학기술대학교 교내학술연구비 지원에 의해 연구되었음.

광운대학교 전자공학과(Department of Electronic Engineering, Kwang-woon University)

<sup>\*</sup>서울과학기술대학교 전자IT미디어공학과(Department of Electronic and IT Media Engineering, Seoul National University of Science and Technology)

<sup>·</sup> Manuscript received March 15, 2017; Revised April 14, 2017; Accepted April 23, 2017. (ID No. 20170315-022)

<sup>·</sup> Corresponding Author: Hyung Chul Park (e-mail: hcpark@seoultech.ac.kr)

인터리빙 샘플링(time interleaved sampling)과 같은 다채널 수신기 기반 기술을 사용한다<sup>[1]~[4]</sup>. 반면, 고속 이동체에 대해서 확장된 탐지 범위와 정밀 분해능 성능을 확보하기위해서는 반복된 UWB 펄스를 이용한 연장된 주사(scanning) 방법이 요구된다. 실제 환경에서는 UWB 펄스의 제한된 송신 전력으로 인해서 수신 신호의 신호대잡음비(SNR: Signal-To-Noise Ratio)가 열화되어 수신 신호 평균을 위한 추가적인 시간이 필요하다. 예를 들어서, 등가 시간 샘플링 방식에서 데이터 평균에 사용되는 펄스 개수가 100개이고, 펄스 반복 주기(PRT: Pulse Repetition Time)이 100 nsec라고 가정하면, 10 m의 탐지 범위와 1 cm 분해능을 위한 레이다의 갱신 주기는 약 10 msec이다. 10 msec의 갱신 주기는 저속 이동체 탐지에는 영향이 없으나, 초고속 이동체의 탐지를 위해서는 갱신 주기의 단축이 불가피하다.

본 논문에서는  $0.18~\mu m$  CMOS 공정에서 제조된  $3\sim5$  GHz UWB IC 기반의 레이다를 설계 및 구현한다. 제안한 UWB 레이다는 기존의 UWB 레이다와 비교해서 장거리의 검출 범위를 가지면서도 검출 결과의 갱신 주기를 짧

게 하여 초고속 이동체를 검출할 수 있다. 더욱이, 제안한 시스템의 응용 분야는 클러터(clutter)가 거의 없어 간섭에 의한 추가적인 성능 열화가 없다. 이에 제안한 시스템에는 다음의 기술들을 제안, 이용한다. 첫째, 채널간 불일치에 대한 보상 시간을 줄이기 위해서 단채널 수신기 구조를 사용한다. 둘째, 동기 수신을 위한 위상 동기 획득 시간을 줄이기 위해서 포락선 검출 기반의 비동기 수신을 사용한다. 셋째, 송신 펄스의 변형에 의한 성능 열화를 방지하기 위해서 디지털 기술을 이용한 임펄스 발생기 회로를 개발, 사용한다.

# II. System Architecture and Function Blocks

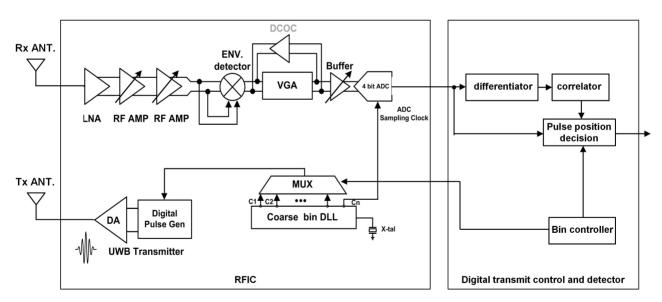

그림 1과 표 1은 제안 시스템의 구조와 규격을 보여준다. 제안 시스템은 UWB 펄스를 레이다 신호로 사용한다. UWB 펄스의 대역폭은 0.5~1 GHz이며, 이 범위에서 조정될 수 있다. 수신기는 등가 시간 샘플링과 포락선 검출방식을 사용하여 1 저장 빈(bin)에 대한 평균을 10 펄스만으로 가능하다!). PRT가 100 nsec이므로 1 빈 데이터 획득

그림 1. 제안 시스템 구조도

Fig. 1. Block diagram of proposed system.

<sup>1) 10</sup> 펄스를 이용하여 평균 필터링을 하면 검출 결과의 갱신주기가 짧아 초고속 이동체 검출은 가능하나, SNR 개선이 제한되는 단점이 있다. 그런데, 개발 시스템의 응용 분야는 클러터가 거의 없어서 클러터와 잡음이 모두 있는 응용분야에 비해서는 원하지 않는 신호의 크기가 작다. 그래서, 평균 필터링을 위한 펄스의 개수가 많이 요구되지 않는다.

| $\overline{\mu}$ | 1  | ᆀ아 | 시스템 | 7.73 |

|------------------|----|----|-----|------|

| #                | Ι. | 세인 | 시스템 | 十二   |

Table 1. Specifications of proposed system.

| Parameter              | Specification |  |

|------------------------|---------------|--|

| Frequency              | 3∼5 GHz       |  |

| Bandwidth              | 0.5~1 GHz     |  |

| Detection range        | < 15 m        |  |

| Resolution             | 15 cm         |  |

| PRT                    | 100 nsec      |  |

| Number of bins         | 100           |  |

| 1 bin acquisition time | 1 $\mu$ sec   |  |

| Total acquisition time | 100 μ sec     |  |

시간은  $1 \mu \text{sec}$ 이다. 표 1에서 보인 바와 같이 15 cm의 분해능을 확보하기 위한 시간 분해능은 1 nsec이다. 제안한 UWB RFIC는 등가 시간 샘플링 구조를 위해서 10 MHz의 기준 주파수와 지연고정루프(DLL: Delay Locked Loop)을 이용하여 1 nsec 간격의 샘플링 클럭을 발생시킨다<sup>[1]</sup>. 한편, RF 회로의 불일치에 의한 오차를 줄이기 위해서 단채널 수신기 회로를 사용한다. PRT가 100 nsec이므로 탐지범위는 15 m이다.

RFIC의 수신기는 RF 전치단(front-end)과 아날로그 신호 처리부(ASP: Analog Signal Processing)로 구성된다. 포락 선 검출 방식은 간섭 신호 또는 소자 불일치에 의한 DC 오프셋에 의한 성능 저하가 발생할 수 있다. 이에 포락선 검출회로 다음에 DC 오프셋 제거 회로(DCOC)를 사용한 다. 아날로그 신호를 디지털로 변환하기 위해서 4-bit 플 래시-타입 아날로그-디지털 변환기(ADC: Analog-to-Digital Converter)를 집적한다. 그림 1에서 보는 바와 같이, ADC 의 샘플링 클럭 위상은 고정되어 있다. 대신 디지털 신호 처리 모듈에서 송신기 펄스 발생 회로의 트리거 클럭 위 상을 1 nsec 단위로 조정한다. 송신기와 수신기의 클럭 위 상차를 이용하여 공간적으로 다른 위치의 데이터 저장 빈을 선택하게 된다. 한편, 송신기는 전력 소모와 회로 크 기를 축소하기 위해서 디지털 회로 합성이 가능한 임펄 스 발생기 구조로 설계한다<sup>[5]</sup>. 임펄스의 주파수와 대역폭 은 디지털 코드를 이용하여 조정이 가능하다.

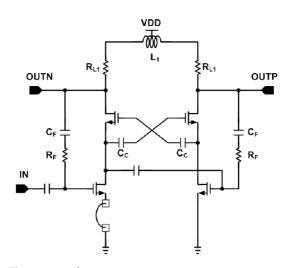

그림 2. LNA 회로도

Fig. 2. LNA circuit diagram.

수신기는 저잡음증폭기(LNA; Low Noise Amplifier), RF 가변 이득 증폭기(VGA; Variable Gain Amplifier), 곱하 기, ASP 블록으로 구성된다. 그림 2에서 보이는 바와 같 이, LNA는 단일입력-차동출력의 저항 피드백의 공통 소 스 구조를 사용한다. 단일입력전압을 차동전압으로 출력 하는 방식을 사용함으로써 공급 전원과 기판잡음에 강인 하고, 짝수 차수 고조파 성분의 왜곡을 감소시킬 수 있다. 한편, 진폭 및 위상 부정합을 감소시키기 위해서 커패시 터를 이용한 상호 결합(cross coupled) 구조를 이용한다. RF VGA는 캐스코드(cascode) 구조인데, 이득 조정을 위해서 부하 스위치를 사용하고, 광대역 특성을 확보하기 위해서 병렬피킹 부하(shunt peaking load)를 사용한다. VGA 출력 은 포락선 검출 회로에 입력된다. 포락선 검출 회로는 길 버트 셀을 이용한 셀프 믹싱의 믹서이다. ASP 블록에 있 는 VGA는 능동 RC 증폭기로서, 3 dB 대역폭은 250 MHz 이고, 이득 조정 범위는 3~42 dB이다2). VGA 출력은 DCOC 회로로 입력된다. DCOC의 cut-off 주파수는 300 kHz 이하 이다. ADC는 1.8 V 전원 전압에서 3 mA의 전류를 소모한 다. DLL 회로는 일반적인 전압제어지연선(VCDL: Voltage Controlled Delay Line)을 사용한다<sup>[1]</sup>. 그림 3은 펄스 발생 기 회로를 보여준다. 펄스 발생기는 단위 시간 지연 셀,

<sup>2)</sup> 개발 시스템의 응용 분야는 대상체의 레이다 반사 면적이 거의 일정한 특징이 있어서 수신 신호의 크기는 거리의 함수이다. 따라서, VGA 이득은 디지털 신호처리 모듈에 있는 bin controller의 제어값에 따라서 조정된다.

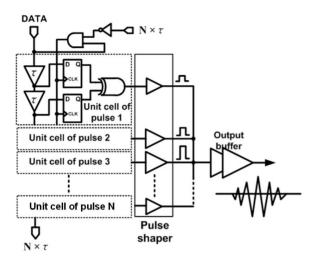

그림 3. 펄스 발생기 구조도

Fig. 3. Block diagram of pulse generator.

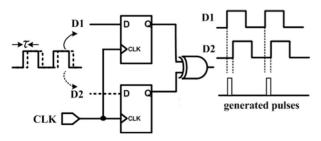

펄스 결합기와 증폭기로 구성된다. 그림 4에서 보이는 바와 같이, 주기  $\tau$ 의 단위 펄스는 XOR 기반의 미분기를 이용하여 발생한다. 이러한 단위 펄스를 결합기를 이용하여 결합하여 UWB 펄스의 주기와 대역폭을 결정한다. 주기  $\tau$ 와 결합되는 펄스의 개수는 조정할 수 있다.

그림 1에는 디지털 신호처리 모듈의 구조도 또한 보여준다. 디지털 신호처리 모듈은 XC3S1500 필드 프로그래 밍 지원 게이트 어레이(FPGA: Field Programmable Gate Array)에 구현한다. 디지털 신호처리 모듈은 두 가지 기능을 수행한다. 첫 번째는 RFIC의 송신기를 제어한다. 그림 1과 앞에서 기술한 바와 같이, RFIC 수신기가 등가 시간샘플링 방식을 사용하는데 ADC의 샘플링 클럭 위상은고정되어 있다. 그래서, 공간적으로 다른 위치의 데이터저장 빈을 선택하기 위해서는 송신기 펄스 발생 회로의

그림 4. 단위 펄스 발생기 Fig. 4. Unit pulse generator.

트리거 클릭 위상을 조정해야 하며, 이 제어 신호를 디지털 신호처리 모듈이 제공한다. 제어 신호는 1 μsec마다 트리거 클릭의 위상을 1 nsec 단위로 변하도록 갱신된다. 두번째는 수신 신호를 이용하여 대상체까지의 거리 정보를 추출한다. 본 연구는 대상체의 이동 속도가 아주 빠르다고 가정한다. 그러므로 수신 신호로부터 거리 정보 추출 까지의 처리 시간이 아주 짧아야 한다. 그런데, 개발 시스템은 클러터가 거의 없는 개활지에서 초고속으로 이동하는 이동체를 탐지하므로 간단한 신호처리 알고리즘 이용이 가능하다. 그림 1의 디지털 신호처리 모듈에서 differentiator와 correlator는 수신 UWB 펄스의 시작 지점, 변곡점, 끝 지점을 검출한다. Pulse position decision 블록에서는 다음과 같은 기준으로 대상체 거리 정보를 추출한다.

첫째, 수신 UWB 펄스의 시작 지점과 변곡점 사이의 전반부 energy( $E_{first\_half}$ )와 변곡점과 끝 지점 사이의 후반부 energy( $E_{second\_half}$ )비가 식 (1)과 같은 특성이 있어야 한다. 본 연구에서는  $V_{low} = 0.75$ ,  $V_{high} = 1.25$ 로 한다.

$$V_{low} < \frac{E_{\text{second half}}}{E_{first half}} < V_{high} \tag{1}$$

둘째, 수신 신호의 최대 크기가 임계값보다 커야 한다. 셋째, 최대 크기를 가지는 위치가 수신 UWB 펄스의 시작 지점과 끝 지점 사이에 있어야 한다.

넷째, 이를 모두 만족하는 수신 UWB 펄스 신호의 최 대 크기 지점을 대상체 거리 정보로 출력하다.

# Ⅲ. 실험 및 결과

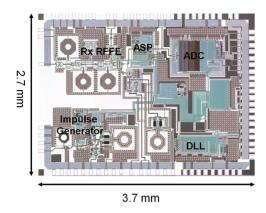

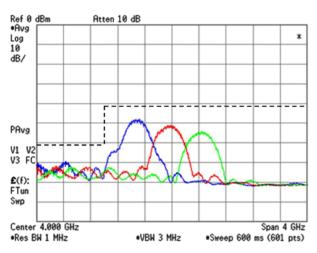

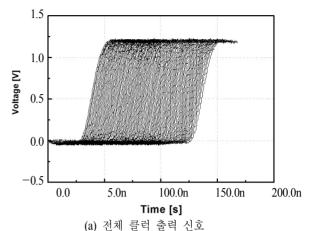

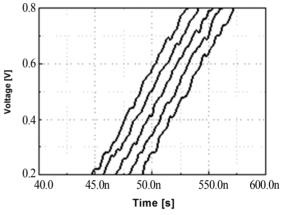

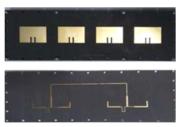

RFIC는 0.18 μm CMOS 공정으로 구현된다. 그림 5에서 보이는 바와 같이, IC의 크기는 3.7×2.7 mm이다. 측정결과, RF 전치단의 이득은 29.5 dB이고, 잡음지수(NF: Noise Figure)는 5.2 dB이다. 그림 6은 출력 UWB 펄스의 스펙트럼 측정 결과를 보여준다. 기술한 바와 같이 신호의 중심주파수가 3.5~4.5 GHz 범위에서 0.5 GHz 단위로 조정되는 것을 볼 수 있다. 또한, 그림 6에서 미국연방통신위원회(FCC: Federal Communications Commission)에서 규정한스펙트럼 마스크를 만족함을 알 수 있다3). RFIC의 전력소모는 1.8 V 전원 전압에서 160 mW이다. 그림 7은 DLL회로의 출력 클럭 신호의 측정 결과를 보여준다. 클럭 신

그림 5. CMOS UWB RFIC 사진

Fig. 5. Photograph of CMOS UWB RFIC.

그림 6. 송신 UWB 펄스 스펙트럼 측정 결과

Fig. 6. Measured spectrum of UWB pulse.

호가 1 nsec 간격으로 조정되는 것을 볼 수 있다.

그림 8은 개발 시스템을 보여준다. 그림 8(a)은 개발 시스템 및 측정환경을 보여준다. 실험은 전파 무향실에서 하며, 레이다 반사 면적(RCS: Radar Cross Section)이 0.1  $m^2$ 인 금속구를 사용한다. 가운데 부분에 비스듬하게 있는 것이 안테나 모듈이다. 안테나 오른쪽에 개발시스템이 있다. 그림 8(b)는 제작한 4×1 패치 배열 안테나를 보여준다. 마이크로스트립 패치 안테나는 6층 타코닉 TLY-5 기판에 구현되며, 측정 결과 이득은 9 dBi이다. 그림 8(c)는

(a) Overall output clock signals

(b) 확대된 클럭 출력 신호

(b) Enlarged output clock signals

그림 7. DLL 출력 클럭 신호의 측정 결과

Fig. 7. Measurement results of DLL output clock signals.

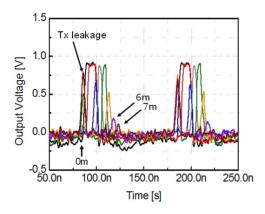

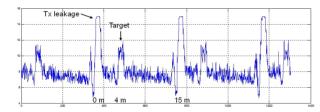

개발한 UWB 레이다 RFIC를 이용한 개발시스템을 보여준다. 그림 9는 유선 루프백 실험 결과를 보여준다. 그림에서 가장 앞선 신호가 송신기의 누설 파형이다. 그 뒤로루프백 경로의 길이에 비례하여 수신 신호가 지연되어수신되는 것을 확인할 수 있다. 그림 10은 그림 8의 환경에서 금속구가 4 m 거리에 위치한 측정 결과로서 펄스 10개로 평균한 수신 신호를 획득하여 MATLAB으로 도시한것이다. 그림 9와 같이 거리 0 m에 큰 송신 누설 신호가

<sup>3)</sup> 그림 6에서 검정색 점선이 FCC에서 규정한 스펙트럼 마스크이다. FCC는 1.99~3.1 GHz 대역에서는 -61.3 dBm/MHz, 3.1~10.6 GHz 대역에서는 -41.3 dBm/MHz를 초과하는 전력으로 송신하지 못하도록 규정하고 있다.

- (a) 측정 환경

- (a) Measurement setup

- (b) 4×1 패치 배열 안테나

- (b) 4×1 patch array antenna

- (c) 개발시스템(RFIC 및 디지털 신호처리 모듈)

- (c) Developed system(RFIC and digital signal processing module)

그림 8. 개발 시스템 및 측정 환경

Fig. 8. Photographs of developed system.

그림 9. 루프백 실험 결과

Fig. 9. Measurement result of loopback test.

그림 10. 무선 실험 결과

Fig. 10. Wireless experimental result.

보임을 알 수 있다. 개발된 UWB 레이다 시스템의 탐지범위는 실험 결과  $0.5\sim7.0$  m이다. 이를 위해서는 이득 조정이 필요하다. 고정된 이득에서는 대상체와의 거리가 가까우면, 수신 신호의 전력이 커서 RF 전치단이 포화되어수신 신호가 왜곡되어 사각파형이 되기 때문이다. 디지털 신호처리 모듈에서의 신호처리 시간은  $50~\mu sec$  이내이

다. 그러므로 15 m 범위의 신호 수신을 포함하여 대상체 거리값 출력까지의 신호처리 시간은 약 150  $\mu$ sec이다.

# Ⅳ. 결 론

본 논문에서는  $0.18~\mu m$  CMOS 공정으로 구현한 단일 칩 UWB 레이다 IC 및 모듈을 제안하고 개발하였다. 검출시간을 단축하기 위해서 포락선 검출 구조를 이용하였다. 또한 1~GHz의 샘플링을 위하여 등가 시간 샘플링 기술을 이용하였다. 실험을 통해서 탐지 범위는  $0.5\sim7.0~m$ 이며, 탐지 분해능은 15~cm임을 확인하였다. 디지털 신호처리를 포함하여 탐지 결과의 갱신 주기는  $150~\mu sec$ 이다. 개발된 UWB 레이다 IC 및 모듈은 음속이상의 초고속 이동체 탐지에 활용할 수 있을 것이다.

#### References

- [1] T. Chu, J. Roderick, S. Chang, T. Mercer, C. Du, and H. Hashemi, "A shortrange UWB impulse-radio CMOS sensor for human feature detection", *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, pp. 294-296, Feb. 2011.

- [2] D. Zito, D. Pepe, M. Mincica, and F. Zito, "A 90 nm CMOS SoC UWB pulse radar for respiratory rate monitoring", *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, pp. 40-41, Feb. 2011.

- [3] H. Hjortland, D. Wisland, T. Lande, C. Limbodal, and K. Meisal, "CMOS impulse radar", IEEE Norchip Conference,

pp. 75-79, Nov. 2006.

- [4] S. Jung, J. Ha, H. Yoo, C. Cheong, Y. Chun, W. Kim, and Y. Eo, "A 3~5 GHz fully integrated CMOS UWB radar chip", Eur. Radar Conference (EuRAD), pp. 57-60, Oct. 2013.

- [5] T. Norimatsu, R. Fujiwara, M. Kokubo, M. Miyazaki, A.

Maeki, Y. Ogata, S. Kobayashi, N. Koshizuka, and K. Sakamura, "A UWB-IR transmitter with digitally controlled pulse generator", IEEE J. Solid-State Circuits, vol. 42, no. 6, pp. 1300-1309, Jun. 2007.

[6] Merrill I. Skolnik, Introduction to Radar Systems, New York, McGraw-Hill, 2001.

#### 상 균 김

2012년 2월: 광운대학교 전자공학과 (공학 사)

2014년 2월: 광운대학교 전자공학과 (공학 석사)

2014년 3월~현재: 광운대학교 전자공학 과 박사과정

[주 관심분야] CMOS RF/아날로그 집적회

로 및 시스템

## 박

1996년 2월: 한국과학기술원 전기 및 전자 공학과 (공학사)

1998년 2월: 한국과학기술원 전기 및 전자 공학과 (공학석사)

2003년 2월: 한국과학기술원 전자전산학 과 (공학박사)

2003년 2월~2005년 2월: 하이닉스반도체

SoC 설계팀 선임연구원

2005년 3월~2010년 2월: 한밭대학교 정보통신컴퓨터공학부 전 임강사/조교수

2010년 3월~현재: 서울과학기술대학교 전자IT미디어공학과 조 교수/부교수

[주 관심분야] 디지털 신호처리 VLSI 설계, 통신 VLSI 설계

1993년 2월: 한국과학기술원 전기 및 전자 공학과 (공학사)

1995년 2월: 한국과학기술원 전기 및 전자 공학과 (공학석사)

2001년 2월: 한국과학기술원 전기 및 전자 공학과 (공학박사)

2000년 8월~2002년 8월: LG전자기술원

RF Team 선임연구원

2002년 9월~2005년 8월: 삼성종합기술원 RF Chip Solution Center 책임연구원

2014년 3월~현재: 광운대학교 전자공학과 교수 2009년 9월~현재: 실리콘알엔디 대표이사 (겸)

[주 관심분야] CMOS RF Transceiver 설계, CMOS Power AMP 설계